# cincoze

# **DS-1200 Series**

# **User Manual**

# **Rugged Embedded Computer**

9/8<sup>th</sup> Generation Intel® Core™ Series Processors High Performance, Expandable and Modular Rugged Embedded Computer

Version: V1.53

# **Contents**

| Pre  | eface                                            |    |

|------|--------------------------------------------------|----|

| Rev  | vision                                           | 05 |

| Cop  | pyright Notice                                   | 05 |

| Ack  | knowledgement                                    | 05 |

| Disc | claimer                                          | 05 |

| Dec  | claration of Conformity                          | 05 |

| Pro  | duct Warranty Statement                          | 06 |

| Tecl | hnical Support and Assistance                    | 07 |

| Con  | nventions Used in this Manual                    | 80 |

| Safe | ety Precaution                                   | 80 |

| Pac  | ckage Contents                                   | 10 |

| Ord  | dering Information                               | 10 |

| Cha  | apter 1 Product Introductions                    |    |

|      | Overview                                         | 12 |

| 1.2  | Highlights                                       | 12 |

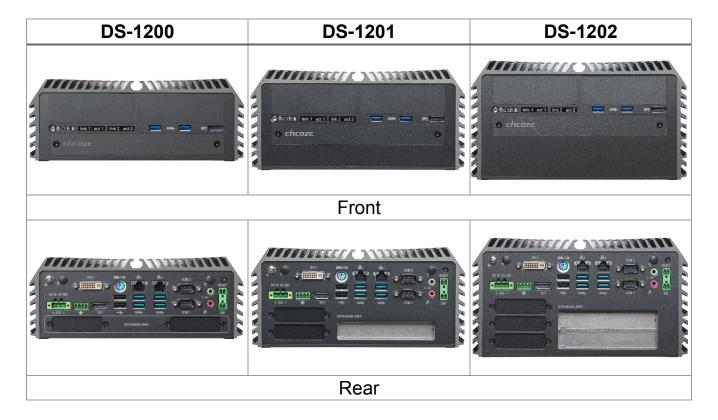

| 1.3  | Product Pictures                                 | 13 |

| 1.4  | Key Features                                     | 13 |

| 1.5  | Hardware Specification                           | 14 |

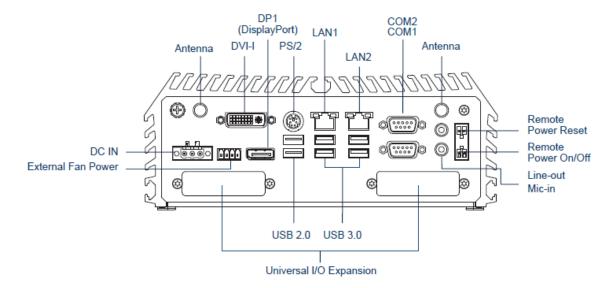

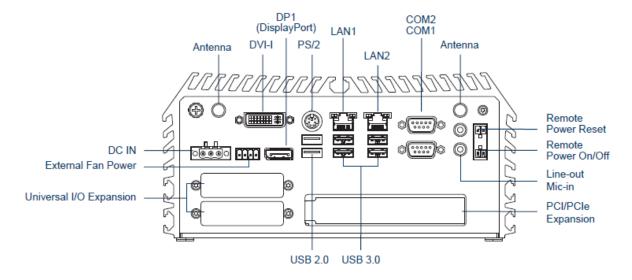

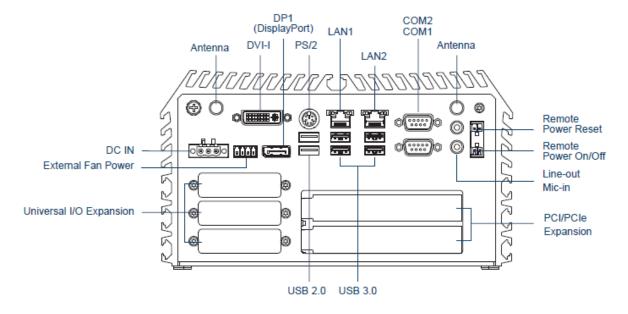

| 1.6  | System I/O                                       | 15 |

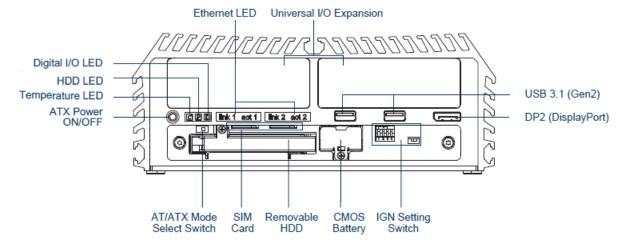

|      | 1.6.1 Front                                      | 15 |

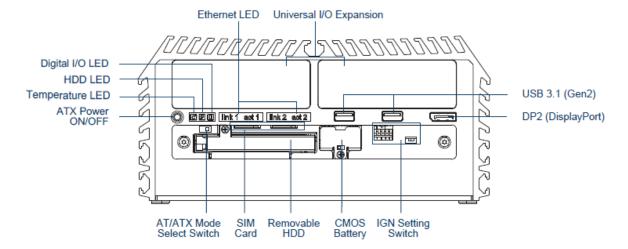

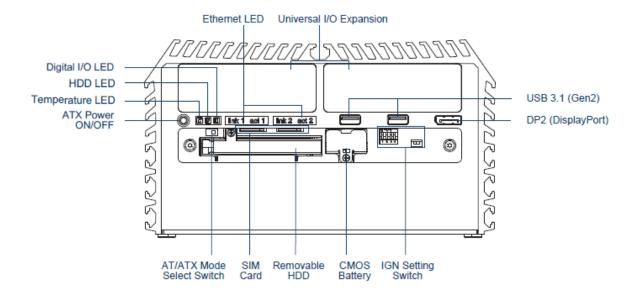

|      | 1.6.2 Rear                                       | 17 |

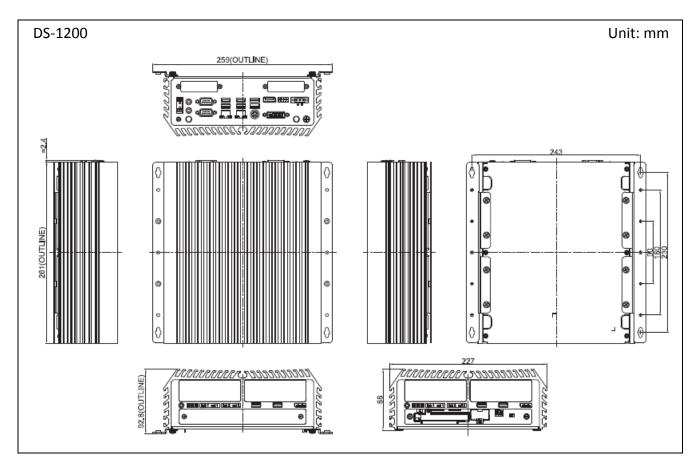

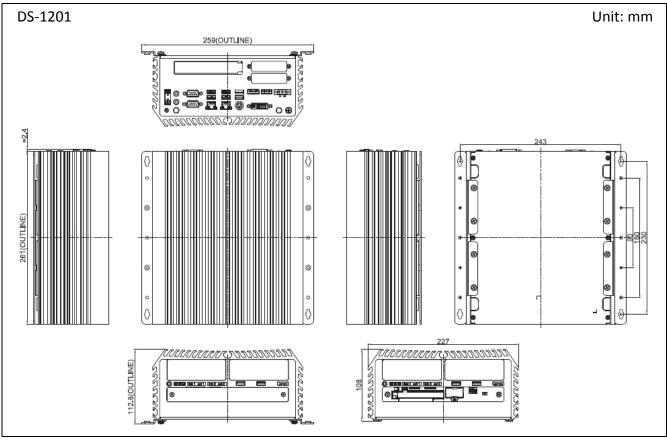

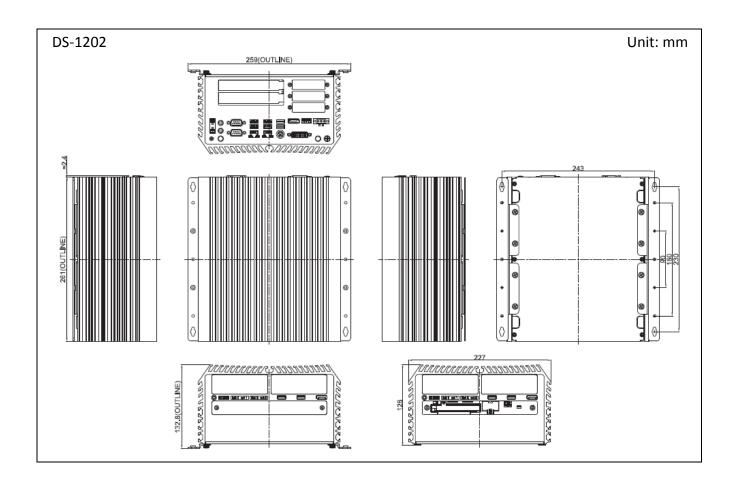

| 1.7  | Mechanical Dimension                             | 19 |

| Cha  | apter 2 Switches and Connectors                  |    |

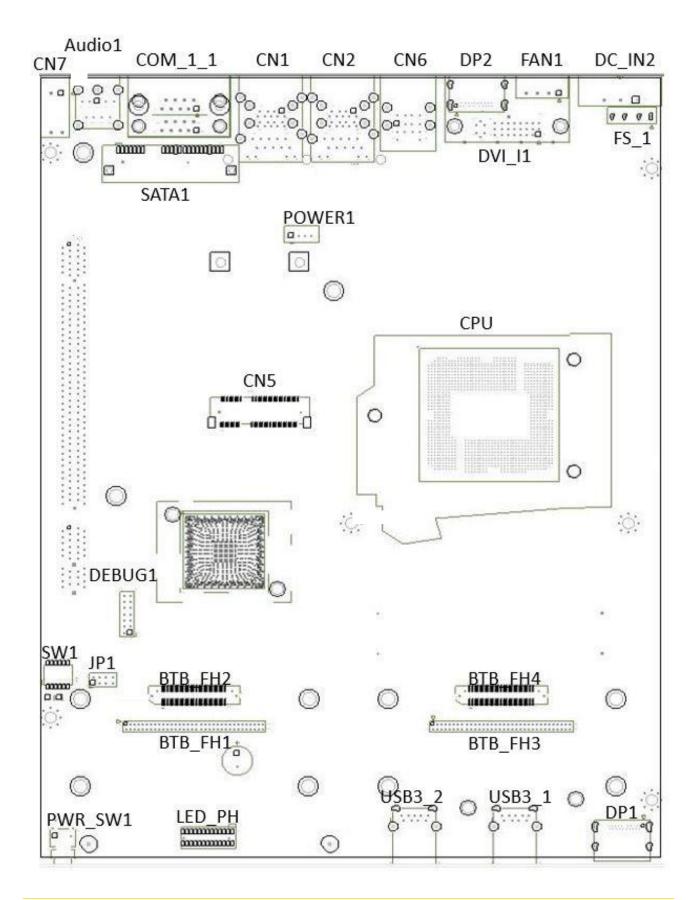

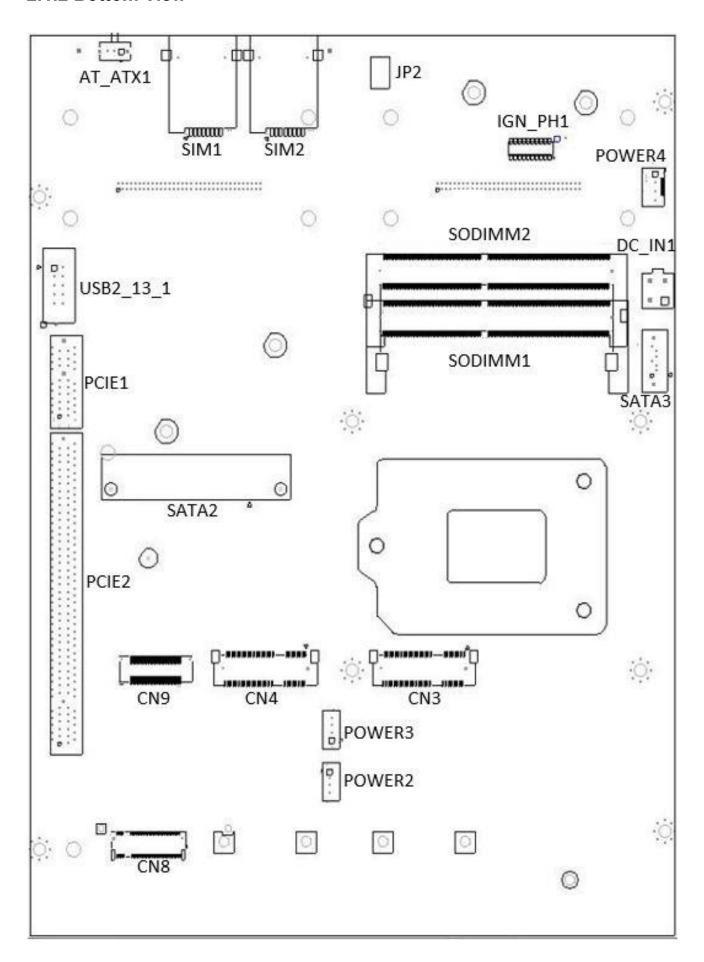

| 2.1  | Location of Switches and Connectors              | 22 |

|      | 2.1.1 Top View                                   | 22 |

|      | 2.1.2 Bottom View                                | 23 |

| 2.2  | Switches and Connectors Definition               | 24 |

| 2.3  | Definition of Switches                           | 25 |

| 2.4  | Definition of Connectors                         | 26 |

| Cha  | apter 3 System Setup                             |    |

|      | Removing the Top Cover                           | 34 |

|      | Installing CPU                                   |    |

| 3.3  | Installing SO-DIMM Memory                        | 40 |

| 3.4  | Installing a Mini-PCIe/mSATA Card on Top Side    | 43 |

| 3.5  | Installing a Mini-PCIe/mSATA Card on Bottom Side | 45 |

| 3.6  | Installing Antennas                              | 46 |

| 3.7        | Installing a SATA Hard Drive on Top Side                         | 49 |

|------------|------------------------------------------------------------------|----|

| 3.8        | Installing an M.2 Card                                           | 51 |

| 3.9        | Installing a PCI/PCIe Add-on Card (For DS-1201 and DS-1202 only) | 53 |

| 3.10       | O Assembling the System                                          | 58 |

| 3.11       | 1 Installing a SATA Hard Drive at Front Side                     | 61 |

| 3.12       | 2 Installing a SIM Card                                          | 64 |

| 3.13       | 3 Installing the CMOS Battery                                    | 65 |

| 3.14       | 4 Fastening the Cover                                            | 67 |

| 3.15       | 5 Wall Mount Brackets                                            | 68 |

| Ch         | apter 4 BIOS Setup                                               |    |

|            | BIOS Introduction                                                | 71 |

|            | Main Setup                                                       |    |

| <b>⊤.∠</b> | 4.2.1 System Date                                                |    |

|            | 4.2.2 System Time                                                |    |

| 4 3        | Advanced Setup                                                   |    |

|            | 4.3.1 CPU Configuration.                                         |    |

|            | 4.3.2 SATA Configuration                                         |    |

|            | 4.3.3 PCH-FW Configuration.                                      |    |

|            | 4.3.4 Trusted Computing                                          |    |

|            | 4.3.5 ACPI Settings                                              |    |

|            | 4.3.6 F81866 Super IO Configuration                              |    |

|            | 4.3.7 Hardware Monitor                                           |    |

|            | 4.3.8 S5 RTC Wake Settings                                       |    |

|            | 4.3.9 Serial Port Console Redirection                            |    |

|            | 4.3.10 USB Configuration                                         | 80 |

|            | 4.3.11 Network Stack Configuration                               |    |

|            | 4.3.12 CSM Configuration                                         | 81 |

|            | 4.3.13 NVMe Configuration                                        | 82 |

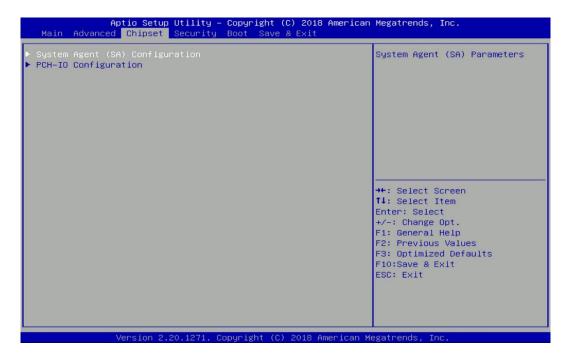

| 4.4        | Chipset Setup                                                    | 83 |

|            | 4.4.1 System Agent (SA) Configuration                            | 83 |

|            | 4.4.2 PCH-IO Configuration                                       | 84 |

| 4.5        | Security Setup                                                   | 87 |

|            | 4.5.1 Administrator Password                                     | 87 |

|            | 4.5.2 User Password                                              | 87 |

| 4.6        | Boot Setup                                                       | 88 |

| 4.7        | Save & Exit                                                      | 89 |

#

# **Preface**

### Revision

| Revision | Description                                            | Date       |

|----------|--------------------------------------------------------|------------|

| 1.00     | First Release                                          | 2018/10/23 |

| 1.10     | Correction Made                                        | 2018/11/20 |

| 1.20     | Update the Supporting Capacity of Memory to the latest | 2019/11/08 |

| 1.30     | Correction Made                                        | 2019/12/18 |

| 1.40     | Add the latest supported processors                    | 2019/12/31 |

| 1.50     | Add CMI-XM12LAN01-R10 installation steps               | 2021/07/26 |

| 1.51     | Correction Made                                        | 2021/08/10 |

| 1.52     | Correction Made                                        | 2021/08/31 |

| 1.53     | Correction Made                                        | 2022/05/31 |

### **Copyright Notice**

© 2018 by Cincoze Co., Ltd. All rights are reserved. No parts of this manual may be copied, modified, or reproduced in any form or by any means for commercial use without the prior written permission of Cincoze Co., Ltd. All information and specification provided in this manual are for reference only and remain subject to change without prior notice.

# **Acknowledgement**

Cincoze is a registered trademark of Cincoze Co., Ltd. All registered trademarks and product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective owners.

### **Disclaimer**

This manual is intended to be used as a practical and informative guide only and is subject to change without notice. It does not represent a commitment on the part of Cincoze. This product might include unintentional technical or typographical errors. Changes are periodically made to the information herein to correct such errors, and these changes are incorporated into new editions of the publication.

### **Declaration of Conformity**

### **FCC**

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

### CE

The product(s) described in this manual complies with all application European Union (CE) directives if it has a CE marking. For computer systems to remain CE compliant, only CE-compliant parts may be used. Maintaining CE compliance also requires proper cable and cabling techniques.

### E-Mark

The "E" mark is based on ECE regulations issued by the Economic Commission for Europe. It is an organizational part of the UN and the members are EU countries and many others. Therefore, the acceptance of approved components is much broader, especially in the eastern part of Europe. It is necessary to confirm whether a particular country has accepted (signed) the application of an ECE-regulation; as the application it is not mandatory for the countries.

# **Product Warranty Statement**

### Warranty

Cincoze products are warranted by Cincoze Co., Ltd. to be free from defect in materials and workmanship for 2 years from the date of purchase by the original purchaser. During the warranty period, we shall, at our option, either repair or replace any product that proves to be defective under normal operation. Defects, malfunctions, or failures of the warranted product caused by damage resulting from natural disasters (such as by lightening, flood, earthquake, etc.), environmental and atmospheric disturbances, other external forces such as power line disturbances, plugging the board in under power, or incorrect cabling, and damage caused by misuse, abuse, and unauthorized alteration or repair, and the product in question is either software, or an expendable item (such as a fuse, battery, etc.), are not warranted.

### **RMA**

Before sending your product in, you will need to fill in Cincoze RMA Request Form and obtain a RMA number from us. Our staff is available at any time to provide you with the most friendly and immediate service.

### RMA Instruction

- Customers must fill in Cincoze Return Merchandise Authorization (RMA)

Request Form and obtain an RMA number prior to returning a defective product to Cincoze for service.

- Customers must collect all the information about the problems encountered and note anything abnormal and describe the problems on the "Cincoze Service Form" for the RMA number apply process.

- Charges may be incurred for certain repairs. Cincoze will charge for repairs to products whose warranty period has expired. Cincoze will also charge for repairs to products if the damage resulted from acts of God, environmental or atmospheric disturbances, or other external forces through misuse, abuse, or unauthorized alteration or repair. If charges will be incurred for a repair, Cincoze lists all charges, and will wait for customer's approval before performing the repair.

- Customers agree to insure the product or assume the risk of loss or damage during transit, to prepay shipping charges, and to use the original shipping container or equivalent.

- Customers can be sent back the faulty products with or without accessories (manuals, cable, etc.) and any components from the system. If the components were suspected as part of the problems, please note clearly which components are included. Otherwise, Cincoze is not responsible for the devices/parts.

- Repaired items will be shipped along with a "Repair Report" detailing the findings and actions taken.

### **Limitation of Liability**

Cincoze' liability arising out of the manufacture, sale, or supplying of the product and its use, whether based on warranty, contract, negligence, product liability, or otherwise, shall not exceed the original selling price of the product. The remedies provided herein are the customer's sole and exclusive remedies. In no event shall Cincoze be liable for direct, indirect, special or consequential damages whether based on contract of any other legal theory.

### **Technical Support and Assistance**

- 1. Visit the Cincoze website at www.cincoze.com where you can find the latest information about the product.

- 2. Contact your distributor or our technical support team or sales representative for technical support if you need additional assistance. Please have following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

### **Conventions Used in this Manual**

√/ARNING

This indication alerts operators to an operation that, if not strictly observed, may result in severe injury.

CAUTION

This indication alerts operators to an operation that, if not strictly observed, may result in safety hazards to personnel or damage to equipment.

NOTE

This indication provides additional information to complete a task easily.

## **Safety Precautions**

Before installing and using this device, please note the following precautions.

- 1. Read these safety instructions carefully.

- 2. Keep this User's Manual for future reference.

- 3. Disconnected this equipment from any AC outlet before cleaning.

- 4. For plug-in equipment, the power outlet socket must be located near the equipment and must be easily accessible.

- 5. Keep this equipment away from humidity.

- 6. Put this equipment on a reliable surface during installation. Dropping it or letting it fall may cause damage.

- 7. Make sure the voltage of the power source is correct before connecting the equipment

- to the power outlet.

- 8. Use a power cord that has been approved for using with the product and that it matches the voltage and current marked on the product's electrical range label. The voltage and current rating of the cord must be greater than the voltage and current rating marked on the product.

- 9. Position the power cord so that people cannot step on it. Do not place anything over the power cord.

- 10. All cautions and warnings on the equipment should be noted.

- 11. If the equipment is not used for a long time, disconnect it from the power source to avoid damage by transient overvoltage.

- 12. Never pour any liquid into an opening. This may cause fire or electrical shock.

- 13. Never open the equipment. For safety reasons, the equipment should be opened only by qualified service personnel.

- If one of the following situations arises, get the equipment checked by service personnel:

- The power cord or plug is damaged.

- Liquid has penetrated into the equipment.

- The equipment has been exposed to moisture.

- The equipment does not work well, or you cannot get it work according to the user's manual.

- The equipment has been dropped and damaged.

- The equipment has obvious signs of breakage.

- 14. CAUTION: Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer.

- 15. Equipment intended only for use in a RESTRICTED ACCESS AREA.

# **Package Contents**

Before installation, please ensure all the items listed in the following table are included in the package.

| Item | Description                                  | Q'ty |

|------|----------------------------------------------|------|

| 1    | Embedded System                              | 1    |

| 2    | Utility DVD Driver                           | 1    |

| 3    | Heat Sink Pack                               | 1    |

| 4    | Screw Pack                                   | 1    |

| 5    | Wall Mounting Kit                            | 1    |

| 6    | Power Terminal Block Connector               | 1    |

| 7    | Remote Power On/Off Terminal Block Connector | 1    |

| 8    | Remote Power Reset Terminal Block Connector  | 1    |

| 9    | Fan Terminal Block Connector                 | 1    |

| 10   | DVI-I to VGA Adaptor                         | 1    |

|      |                                              |      |

Note: Notify your sales representative if any of the above items are missing or damaged.

# **Ordering Information**

| Model No.   | Product Description                                   |

|-------------|-------------------------------------------------------|

|             | 9/8th Generation Intel® Core™ Series Processors, High |

| DS-1200-R10 | Performance, Expandable and Modular Rugged Embedded   |

|             | Computer                                              |

|             | 9/8th Generation Intel® Core™ Series Processors, High |

| DS-1201-R10 | Performance, Expandable and Modular Rugged Embedded   |

|             | Computer with 1x PCI/PCIe Expansion Slots             |

|             | 9/8th Generation Intel® Core™ Series Processors, High |

| DS-1202-R10 | Performance, Expandable and Modular Rugged Embedded   |

|             | Computer with 2x PCI/PCIe Expansion Slots             |

# **Chapter 1 Product Introductions**

### 1.1 Overview

DS-1200 series is a high performance fanless embedded computer, powered by 9/8th generation Intel® Core™ processor (Coffee Lake) with up to 8 cores and 64GB DDR4 memory capacity for unprecedented performance to fulfill all kinds of high-end computing requirements. The system also incorporates rich I/O, such as 2x Intel® GbE ports, 2x USB 3.1 (Gen2), 4x USB 3.0, 1x DVI-I, 2x DisplayPort, and 1x M.2 Key M 2280 socket for ultra-fast data transfer speed.

Based on Cincoze' innovative CMI & CFM Technology, it allows users to expand I/O and functionalities through ready-to-use modules, such as GbE/PoE ports, serial ports, optical isolated digital I/O and power ignition function. Furthermore, DS-1200 series supports maximum 2 PCI(e) expansion slots to accommodate versatile add-on cards.

Designed to operate under harsh conditions, DS-1200 series has passed rigorous testing like EN50155 (EN50121-3-2) and EN62368-1 to fulfill industrial applications such as rolling stock. Besides, DS-1200 series features with wide operating temperature (-40°C to 70°C), wide range DC power input (from 9V to 48V), high tolerance of shock/vibration (5G/50G), and industrial-grade protections (OVP, OCP, ESD Surge, ...etc).

# 1.2 Highlights

### **High Performance**

The new 9/8th generation Intel® Core™ processor (Coffee Lake) offers for the first time up to 8 cores, 16 threads and 1.4 times computing performance improvement comparing to the previous generation (Kaby Lake).

### Fully Modular and Expandable

Featuring PCI/PCIe expansion slots, Mini-PCIe slots, CMI (Combined Multiple I/O), CFM (Control Function Module), and versatile ready-to-use modules, DS-1200 series provides great flexibility to configure the system according to your need.

### Wide Temperature

DS-1200 series is designed for continuous operation in wide temperature range from -40°C to 70°C. In addition, it also features with anti-shock/vibration and ESD/surge protection for tough industrial environments.

# 1.3 Product pictures

# 1.4 Key Features

- Supports 9/8th Gen Intel® Core™ / Pentium® / Celeron® Octa Cores 35W/65W LGA 1151 Processors

- 2x DDR4 SO-DIMM Socket, Supports Up to 2666MHz, 64GB

- Triple Independent Displays: 1x DVI-I and 2x DP (4K Resolution)

- 1x M.2 2280 M Key Socket, Auto-detection for PClex4 NVMe SSD or SATA Gen3 SSD

- 2x Front Accessible SIM Card Slots for Signal Redundancy

- 2x PCI/PCIe Slots for Add-on Cards (Maximum Length: 235mm) (For DS-1201 & DS-1202 only)

- 4x CMI Slots for Modular I/O Expansions

- 1x CFM Slot for Power Ignition Sensing Function

- Wide Operating Temperature (-40°C to 70°C)

- EN50155 (EN50121-3-2) / EN62368-1 Certified

# 1.5 Hardware Specification

#### **Processor**

- 9th Generation Intel® Coffee Lake-R S Series CPU:

- Intel® Core™ i7-9700E 8 Cores Up to 4.4 GHz, TDP 65W

- Intel® Core™ i5-9500E 6 Cores Up to 4.2 GHz, TDP 65W

- Intel® Core™ i3-9100E 4 Cores Up to 3.7 GHz, TDP 65W

- Intel® Core™ i7-9700TE 8 Cores Up to 3.8 GHz, TDP 35W

- Intel® Core™ i5-9500TE 6 Cores Up to 3.6 GHz. TDP 35W

- Intel® Core™ i3-9100TE 4 Cores Up to 3.2 GHz, TDP 35W

- 8th Generation Intel® Coffee Lake S Series CPU:

- Intel® Core™ i7-8700 6 Cores Up to 4.6 GHz 12M Cache, TDP 65W

- Intel® Core™ i5-8500 6 Cores Up to 4.1 GHz 9M Cache, TDP 65W

- Intel® Core™ i3-8100 4 Cores 3.6 GHz 6M Cache, TDP 65W

- Intel® Core™ i7-8700T 6 Cores Up to 4.0 GHz 12M Cache, TDP 35W

- Intel® Core™ i5-8500T 6 Cores Up to 3.5 GHz 9M Cache, TDP 35W

- Intel® Core™ i3-8100T 4 Cores 3.1 GHz 6M Cache, TDP 35W

- Intel® Pentium® G5400 2 Cores 3.7 GHz 4M Cache, TDP 58W

- Intel® Pentium® G5400T 2 Cores 3.1 GHz 4M Cache, TDP 35W

- Intel® Celeron® G4900 2 Cores 3.1 GHz 2M Cache, TDP 54W

- Intel® Celeron® G4900T 2 Cores 2.9 GHz 2M Cache, TDP 35W

### Chipset

• Intel® Q370

### **BIOS**

• AMI 32MB SPI BIOS

#### Memory

- 2x DDR4-2400/2666 MHz SO-DIMM Sockets, Supports up to 64 GB (Un-buffered and Non-ECC Type)

- \* DDR4 2666MHz memory modules are only for Core™ i7/i5 Processors

### Graphics

- Integrated Intel® UHD Graphics 630: Core™ i7/i5/i3

- Integrated Intel® UHD Graphics 610: Pentium® /Celeron®

- Supports Triple Independent Display (1x DVI-I, 2x DisplayPort)

### **Audio**

- Realtek® ALC888

- · High Definition Audio

### External I/O Interface

- 1x DVI-I (DVI-D: 1920 x 1200 @60Hz / VGA: 1920 x 1080 @60Hz)

- 2x DisplayPort (DisplayPort: 4096 x 2304 @60Hz)

- ullet 2x GbE LAN (Supports WoL, Teaming, Jumbo Frame & PXE), RJ45

- GbE1: Intel® I210

- GbE2: Intel® I219-LM

- 2x USB 3.1 Gen2 (Type A)

- 4x USB 3.0 (Type A)

- 2x USB 2.0 (Type A)

- 2x RS-232/422/485 with Auto Flow Control (Supports 5V/12V), DB9

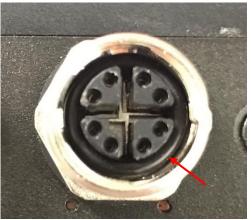

- 1x PS/2, 6-pin mini-DIN Female Connector

- 1x Line-out & 1x Mic-in, Phone Jack 3.5mm

- 1x ATX Power On/Off Button

- 1x AT/ATX Mode Switch

- 1x Clear CMOS Switch

- 1x Remote Reset Connector, 2-pin Terminal Block

- 1x Remote Power On/Off Connector, 2-pin Terminal Block

- 1x External Fan Connector, 4-Pin Terminal Block (Supports smart fan by BIOS)

### Storage

- 2x 2.5" SATA HDD/SSD bay (Gen3), 1x Internal, 1x Front Accessible Supports RAID 0/1

- 3x mSATA (shared by Mini-PCle socket) (Gen3), BIOS Selectable

- 1x M.2 Key M 2280 Socket, Supports PCIe x4 NVMe SSD or SATA SSD (Gen3)

### **Expansion**

• 3x Full-size Mini-PCle Socket

- 2x SIM Socket

- 1x CFM (Control Function Module) Interface

- 2x CMI (Combined Multiple I/O) High Speed Interface

- 2x CMI (Combined Multiple I/O) Low Speed Interface

- 2x Antenna Hole

- 1x PCI/PCle Expansion slot (with Optional Riser Card) (For DS-1201)

- \* Supports maximum dimensions of add-on card (H x L):110 x 237mm

- 2x PCI/PCle Expansion slot (with Optional Riser Card) (For DS-1202)

- \* Supports maximum dimensions of add-on card (H x L):110 x 237mm

### Other Function

- Supports Instant Reboot Technology (0.2 sec)

- SuperCap Integrated for CMOS Battery Maintenance-free Operation

- Watchdog Timer: Software Programmable Supports 256 Levels System Reset

### **Power Requirement**

- Supports AT/ATX Power Type

- Power Input Voltage 9-48VDC

- 1x 3-Pin Terminal Block

- Power Adapter AC/DC 24V/5A 120W or 24V/9.2A 220W (Optional)

### **Physical**

• Dimensions (WxDxH):

227 x 261 x 88 mm (DS-1200), 227 x 261 x 108 mm (DS-1201) 227 x 261 x 128 mm (DS-1202)

- Weight: 4.3 kg (DS-1200), 4.92 kg (DS-1201), 5.14 kg (DS-1202)

- · Construction: Extruded Aluminum with Heavy Duty Metal

- Mounting: Wall MountFanless Design

- Unibody ChassisJumper-less Design

### **Protection**

- Reverse Power Input Protection

- Over Voltage Protection

- Protection Range: 51-58V

- Protection Type: shut down operating voltage, re-power on at the present level to recover

- Over Current Protection: 15A

- ESD Protection: +/-8kV (air), +/-4kV (contact)

- Surge Protection: 2 kV

### **Operating System**

- Windows® 10

- Linux: Supports by project

### Environment

• Operating Temperature:

35W TDP Processor: -40°C to 70°C

51~65W TDP Processor: -40°C to 45°C

- \* PassMark BurnInTest: 100% CPU, 2D/3D Graphics (without thermal throttling)

- \* With extended temperature peripherals; Ambient with air flow

- \* According to IEC60068-2-1, IEC60068-2-2, IEC60068-2-14

- Storage Temperature: -40°C to 85°C

- Relative Humidity: 95%RH @ 70°C (non-Condensing)

- Shock: Operating, 50 Grms, Half-sine 11 ms Duration (w/ SSD, according to IEC60068-2-27)

- Vibration: Operating, 5 Grms, 5-500 Hz, 3 Axes (With SSD, according to IEC60068-2-64)

- MTBF: 396,565 Hours

### Certification

- EMC: CE, FCC Class A

- Safety: LVD, EN62368-1

- Railway: EN50155, EN50121-3-2

- \* Product Specifications and features are for reference only and are subject to change without prior notice. For more information, please refer to the latest product datasheet from Cincoze's website.

# 1.6 System I/O

### 1.6.1 Front

### **ATX Power On/Off**

Used to power-on or power-off the system

### **AT/ATX Mode Select Switch**

Used to select AT or ATX power mode

### **Power LED**

Indicates the power status of the system

### **Temperature LED**

Indicates the temperature of the system

### **HDD LED**

Indicates the status of the hard drive

### Digital I/O LED

Indicates the working status of digital input/output

### **Ethernet LED**

Indicates the status of the LAN ports

### **USB 3.1 Port**

Used to connect USB 3.1/3.0/2.0/1.1 device

### **DisplayPort**

Used to connect the system with DisplayPort monitor

# SIM card, CMOS Battery, and 2.5" Removable HDD Bay

Used to inserts a SIM card, CMOS battery, and 2.5" HDD

### **DS-1201**

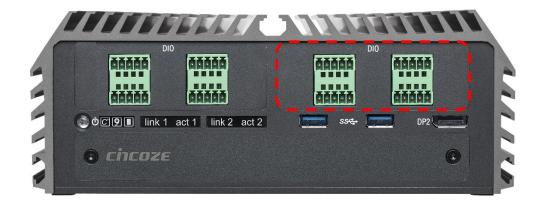

### 1.6.2 Rear

### **DC IN Terminal Block**

Used to plug a DC power input with terminal block

### **External Fan Terminal Block**

Used to plug an external fan with terminal block

### **DVI-I Port**

Used to connect a DVI monitor or connect optional split cable for dual display mode

### PS/2 Port

Used to connect the PS/2 device

### **LAN Port**

Used to connect to local area network

### **Display Port**

Used to connect a monitor with DisplayPort interface

### **USB 3.0 Port**

Used to connect USB 3.0/2.0/1.1 device

### **USB 2.0 Port**

Used to connect USB 2.0/1.1 device

### **Antenna Hole**

Used to connect an antenna for optional wireless module

### **COM Port**

Used to connect to RS-232/422/485 serial devices

### Line-Out

Used to connect a speaker

### Mic-In

Used to connect a microphone

### Remote Power On/Off & Remote Power

### **Reset Terminal Block**

A terminal block used to connect to remote power on/off switch

### **Universal I/O Bracket**

Used to customized I/O output

### **DS-1201**

# **1.7 Mechanical Dimension**

**Chapter 2**Switches &

Connectors

# 2.1 Location of Switches and Connectors

### **2.1.1 Top View**

### 2.1.2 Bottom View

# 2.2 Switches and Connectors Definition

### **List of Switch and Connectors**

| Location         | Definition                                               |

|------------------|----------------------------------------------------------|

| SW1              | RTC / SATA DOM / COM1 / COM2 Power Select                |

| JP1              | BIOS SPI interface (Optional)                            |

| JP2              | RTC Battery board to board connector                     |

| AT_ATX1          | AT / ATX Power Mode Switch                               |

| Debug1           | Engineer Use / LPC 80 Port interface (Optional)          |

| PWR_SW1          | Power Button, System LED                                 |

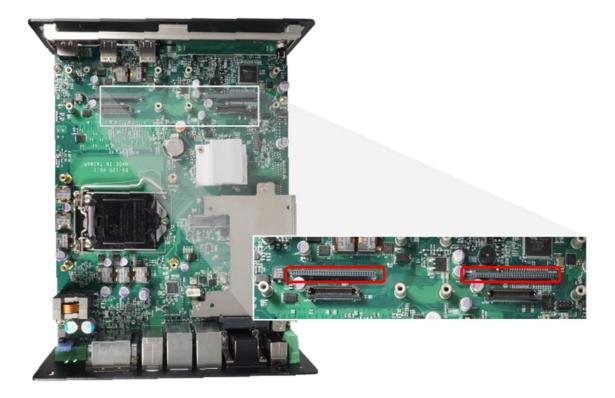

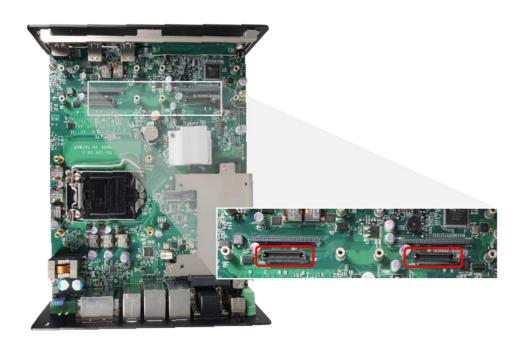

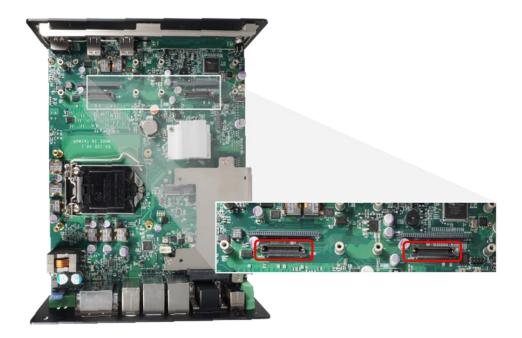

| BTB_FH1, BTB_FH3 | DIO + COM Port Board to Board Connector                  |

| BTB_FH2, BTB_FH4 | PSE LAN Port Board to Board Connector                    |

| IGN_PH1          | IGN Board to Board connector                             |

| FS1              | Input Fuse 15A                                           |

| DC_IN1           | 4-PIN DC Out                                             |

| DC_IN2           | 3-PIN DC 9-48V Power Input with Power Ignition Connector |

| FAN1             | External PWM Fan Connector                               |

| DP1, DP2         | DisplayPort Connector                                    |

| DVI_I1           | DVI-I Connector                                          |

| CN6              | PS/2 and USB 2.0 Ports                                   |

| CN1              | LAN1 and USB 3.0 Ports                                   |

| CN2              | LAN2 and USB 3.0 Ports                                   |

| COM_1_1          | COM1 / COM2, RS232 / RS422 / RS485 Connector             |

| AUDIO1           | Audio Jack / MIC_IN / LINE_OUT                           |

| CN7              | Remote Power on/off, Remote Reset Switch Connector       |

| USB3_1, USB3_2   | USB 3.1 Ports                                            |

| SIM1, SIM2       | SIM Card Socket                                          |

| SATA1, SATA2     | 22 Pin SATA Connector                                    |

| SATA3            | SATA Connector                                           |

| Power 1~4        | Power Connector                                          |

| CN5              | Mini PCI-Express Socket + mSATA + 4G Module              |

| CN3, CN4         | Mini PCI-Express / mSATA Socket                          |

| CN8              | M.2 PCIE / SATA SSD                                      |

| USB2_13_1        | Internal USB 2.0 Ports                                   |

| PCIE1            | PCI-Express X1 Socket                                    |

| PCIE2            | PCI-Express X16 Socket                                   |

| SODIMM1, SODIMM2 | DDR4 SODIMM Socket                                       |

# 2.3 Definition of Switches

### AT\_ATX1: AT / ATX Power Mode Switch

| Switch      | Definition               |

|-------------|--------------------------|

| 1-2 (Right) | ATX Power Mode (Default) |

| 2-3 (Left)  | AT Power Mode            |

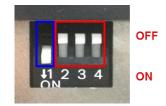

# SW1: RTC / SATA DOM / COM1 / COM2 Power Select Super CAP Function Setting: Pin Define SW1 Switch

| Switch mode | Function  | ON                  | OFF     |

|-------------|-----------|---------------------|---------|

| 1           | Super CAP | Enable<br>(Default) | Disable |

### **SATA DOM Function Setting: Pin Define SW1 Switch**

| Switch mode | Function | ON                | OFF    |

|-------------|----------|-------------------|--------|

| 2           | SATA DOM | Disable (Default) | Enable |

## COM1/2 Voltage Function Setting: Pin Define SW1 Switch

| Switch<br>mode | Function |        | ON OFF          |      |

|----------------|----------|--------|-----------------|------|

|                | COM1     | 0V(RI) | ON/ON (Default) |      |

| 3-4            |          | 5V     | ON/OFF          |      |

|                |          | 12V    | OFF/OFF         |      |

|                |          | 0V(RI) | ON/ON (Defa     | ult) |

| 5-6            | COM2     | 5V     | ON/OFF          |      |

|                |          | 12V    | OFF/OFF         |      |

# 2.4 Definition of Connectors

CN5: Mini PCI-Express Socket (Support mSATA and SIM Card to Link feature)

| Pin | Definition       | Pin | Definition  | Pin | Definition |

|-----|------------------|-----|-------------|-----|------------|

| 1   | WAKE#            | 19  | SIM_DATA2   | 37  | RESERVED   |

| 2   | 3.3V             | 20  | 3.3V        | 38  | USB_D+     |

| 3   | NA               | 21  | GND         | 39  | RESERVED   |

| 4   | GND              | 22  | PERST#      | 40  | GND        |

| 5   | NA               | 23  | PERN/SATARP | 41  | 3.3V       |

| 6   | 1.5V             | 24  | 3.3V        | 42  | NA         |

| 7   | UIM_RST2         | 25  | PERP/SATARN | 43  | GND        |

| 8   | SIM_PWR1         | 26  | GND         | 44  | NA         |

| 9   | GND              | 27  | GND         | 45  | NA         |

| 10  | SIM_DATA1        | 28  | +1.5V       | 46  | NA         |

| 11  | REFCLK-          | 29  | GND         | 47  | NA         |

| 12  | SIM_CLK          | 30  | SMB_CLK     | 48  | +1.5V      |

| 13  | REFCLK+/SIM_PWR2 | 31  | PETN/SATATN | 49  | NA         |

| 14  | SIM_Reset1       | 32  | SMB_DATA    | 50  | GND        |

| 15  | GND              | 33  | PETP/SATAPN | 51  | NA         |

| 16  | SIM_VPP1         | 34  | GND         | 52  | +3.3V      |

| 17  | SIM_CLK2         | 35  | GND         |     |            |

| 18  | GND              | 36  | USB_D-      |     |            |

# CN4 : Mini PCI-Express Socket (Support mSATA feature)

| Pin | Definition | Pin | Definition   | Pin | Definition |

|-----|------------|-----|--------------|-----|------------|

| 1   | WAKE#      | 19  | NA           | 37  | GND        |

| 2   | 3.3V       | 20  | 3.3V         | 38  | USB_D+     |

| 3   | NA         | 21  | GND          | 39  | 3.3V       |

| 4   | GND        | 22  | PERST#       | 40  | GND        |

| 5   | NA         | 23  | PERN/SATARXP | 41  | 3.3V       |

| 6   | 1.5V       | 24  | 3.3V         | 42  | NA         |

| 7   | NA         | 25  | PERPSATARXN  | 43  | GND        |

| 8   | NA         | 26  | GND          | 44  | NA         |

| 9   | GND        | 27  | GND          | 45  | NA         |

| 10  | NA         | 28  | +1.5V        | 46  | NA         |

| 11  | NA         | 29  | GND          | 47  | NA         |

| 12  | NA         | 30  | SMB_CLK      | 48  | +1.5V      |

| 13  | NA         | 31  | PETN/SATATXN | 49  | NA         |

| 14  | NA         | 32  | SMB_DATA     | 50  | GND        |

| 15  | GND        | 33  | PETP/SATATXP | 51  | NA         |

| 16  | NA         | 34  | GND          | 52  | +3.3V      |

| 17  | NA         | 35  | GND          |     |            |

| 18  | GND        | 36  | USB_D-       |     |            |

# CN3: Mini PCI-Express Socket (Support mSATA feature)

|     | <u> </u>   |     | <u> </u>    |     | <u> </u>   |

|-----|------------|-----|-------------|-----|------------|

| Pin | Definition | Pin | Definition  | Pin | Definition |

| 1   | WAKE#      | 19  | NA          | 37  | GND        |

| 2   | 3.3V       | 20  | 3.3V        | 38  | USB_D+     |

| 3   | NA         | 21  | GND         | 39  | 3.3V       |

| 4   | GND        | 22  | PERST#      | 40  | GND        |

| 5   | NA         | 23  | PERN/SATARP | 41  | 3.3V       |

| 6   | 1.5V       | 24  | +3.3VAUX    | 42  | NA         |

| 7   | CLKREQ#    | 25  | PERP/SATARN | 43  | GND        |

| 8   | NA         | 26  | GND         | 44  | NA         |

| 9   | GND        | 27  | GND         | 45  | NA         |

| 10  | NA         | 28  | +1.5V       | 46  | NA         |

| 11  | REFCLK-    | 29  | GND         | 47  | NA         |

| 12  | NA         | 30  | SMB_CLK     | 48  | +1.5V      |

| 13  | REFCLK+    | 31  | PETN/SATATN | 49  | NA         |

| 14  | NA         | 32  | SMB_DATA    | 50  | GND        |

| 15  | GND        | 33  | PETP/SATATP | 51  | NA         |

| 16  | NA         | 34  | GND         | 52  | +3.3V      |

| 17  | NA         | 35  | GND         |     |            |

| 18  | GND        | 36  | USB_D-      |     |            |

# CN8: M.2 Socket Socket (Support M.2 PCIE / SATA SSD feature)

| Pin | Definition Definition | Pin | Definition    | Pin | Definition |

|-----|-----------------------|-----|---------------|-----|------------|

| 1   | CFG3                  | 27  | GND           | 53  | REFCLKN    |

| 2   | +3.3V                 | 28  | NC            | 54  | PEWAKE#    |

| 3   | GND                   | 29  | PERN1         | 55  | REFCLKP    |

| 4   | +3.3V                 | 30  | NC            | 56  | NC         |

| 5   | PERN3                 | 31  | PERP1         | 57  | GND        |

| 6   | NC                    | 32  | NC            | 58  | NC         |

| 7   | PERP3                 | 33  | GND           | 59  | key        |

| 8   | NC                    | 34  | NC            | 60  | key        |

| 9   | GND                   | 35  | PETN1         | 61  | key        |

| 10  | LED                   | 36  | NC            | 62  | key        |

| 11  | PETN3                 | 37  | PETP1         | 63  | key        |

| 12  | +3.3V                 | 38  | DEVSLP        | 64  | key        |

| 13  | PETP3                 | 39  | GND           | 65  | key        |

| 14  | +3.3V                 | 40  | SMB_CLK       | 66  | key        |

| 15  | GND                   | 41  | PERN0/SATARP0 | 67  | NC         |

| 16  | +3.3V                 | 42  | SMD_DATA      | 68  | SUSCLK     |

| 17  | PERN2                 | 43  | PERP0/SATARN0 | 69  | PEDET      |

| 18  | +3.3V                 | 44  | ALERT#        | 70  | +3.3V      |

| 19  | PERP2                 | 45  | GND           | 71  | GND        |

| 20  | NC                    | 46  | NC            | 72  | +3.3V      |

| 21  | CFG0                  | 47  | PETN0/SATATN0 | 73  | GND        |

| 22  | NC                    | 48  | NC            | 74  | +3.3V      |

| 23  | PETN2                 | 49  | PETP0/SATATP0 | 75  | CFG2       |

| 24  | NC                    | 50  | RESET#        | 76  | NC         |

| 25  | PETP2                 | 51  | GND           |     |            |

| 26  | NC                    | 52  | NC            |     |            |

### **SATA3: SATA Connector (SATA DOM)**

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | GND        | 5   | RX2-       |

| 2   | TX2+       | 6   | RX2+       |

| 3   | TX2-       | 7   | NC/+5V     |

| 4   | GND        |     |            |

### POWER1, POWER2, POWER3: Power Connector

Connector Type: 1X4-pin Wafer, 2.0 mm pitch

| Pin | Definition |

|-----|------------|

| 1   | +5V        |

| 2   | GND        |

| 3   | GND        |

| 4   | +12V       |

1 2 3 4

### **POWER4: Power Connector**

Connector Type: 1X4-pin Wafer, 2.54mm pitch

| Pin | Definition |

|-----|------------|

| 1   | +5V        |

| 2   | GND        |

| 3   | GND        |

| 4   | +12V       |

1 2 3 4

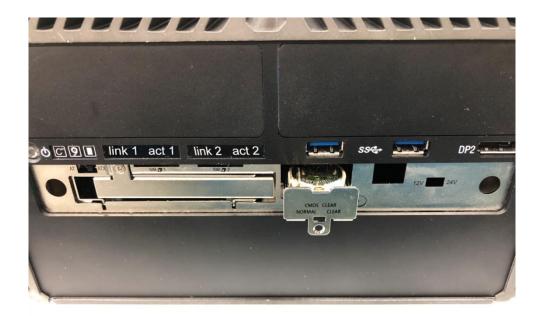

### CLR\_CMOS1: Clear BIOS Switch

| Pin         | Definition              |

|-------------|-------------------------|

| 1-2 (Left)  | Normal Status (Default) |

| 2-3 (Right) | Clear BIOS              |

### PWR\_SW1: Power on/ off switch and Thermal LED

| Button  | Definition |

|---------|------------|

| ON      | Green      |

| OFF     | Blue       |

| Thermal | Red        |

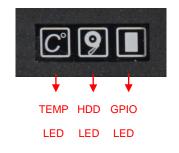

### LED\_PH: TEMP / HDD / GPIO LED Status

| LED B1   | Status                    | LED Color       |

|----------|---------------------------|-----------------|

| HDD LED  | HDD Read/Write            | Blinking Yellow |

|          | System Temp ≤ 65°C        | Colorless       |

| TEMPLED  | 65°C < System Temp ≤ 70°C | Blue            |

| TEMP LED | 70°C < System Temp ≤ 75°C | Red             |

|          | 75°C < System Temp        | Blinking Red    |

The TEMP LED is only available when IGN module is installed.

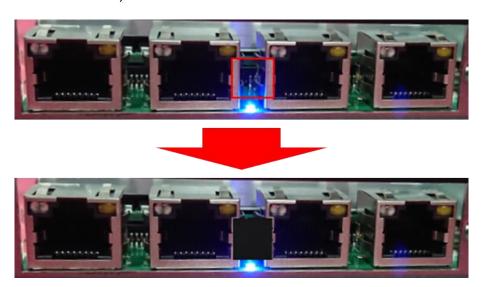

### **LAN LED Status Defines**

| Act LED Status  | Definition    | Link LED Status | Definition           |

|-----------------|---------------|-----------------|----------------------|

| Blinking Yellow | Data Activity | Steady Green    | 1Gbps Network Link   |

| Off             | No Activity   | Steady Orange   | 100Mbps Network Link |

|                 |               | Off             | 10Mbps Network Link  |

### DC\_IN2: DC Power Input Connector (+9-48V)

Connector Type: Terminal Block 1x3 3-pin, 5.0mm pitch

| Pin | Definition     |

|-----|----------------|

| 1   | +9-48VIN       |

| 2   | Ignition (IGN) |

| 3   | GND            |

Please disconnect the power source before mounting the DC power cables or connecting the DC power connector to system.

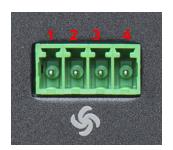

### **FAN1: External PWM Fan Connector**

Connector Type: Terminal Block 1X4 4-pin, 3.5mm pitch

| Pin | Definition |

|-----|------------|

| 1   | GND        |

| 2   | +12V       |

| 3   | SENSE      |

| 4   | Control    |

### CN7: Remote Power on/off, Remote Reset Switch Connector

Connector Type: Terminal Block 2X2 4-pin, 3.5mm pitch

| Pin | Definition |

|-----|------------|

| 1   | PWR_SW     |

| 2   | RESET_SW   |

| 3   | GND        |

| 4   | GND        |

Do not apply power to this connector!

This port is used to connect a SWITCH!

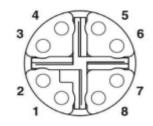

### COM1\_2\_1: RS232 / RS422 / RS485 Connector

Connector Type: 9-pin D-Sub

| Pin | RS232<br>Definition | RS422 / 485<br>Full Duplex<br>Definition | RS485<br>Half Duplex<br>Definition |

|-----|---------------------|------------------------------------------|------------------------------------|

| 1   | DCD                 | TX-                                      | DATA -                             |

| 2   | RXD                 | TX+                                      | DATA +                             |

| 3   | TXD                 | RX+                                      |                                    |

| 4   | DTR                 | RX-                                      |                                    |

| 5   |                     | GND                                      |                                    |

| 6   | DSR                 |                                          |                                    |

| 7   | RTS                 |                                          |                                    |

| 8   | CTS                 |                                          |                                    |

| 9   | RI                  |                                          |                                    |

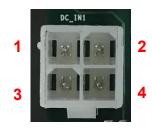

### DC\_IN1: 4 PINs DC 9-48V Power Connector

Connector Type: 2x2 4-pin, 4.2mm pitch

| Pin | Definition |

|-----|------------|

| 1   | GND        |

| 2   | GND        |

| 3   | +9-48VIN   |

| 4   | +9-48VIN   |

WARNING

Before using this connector, make sure that the PIN3 & PIN4 voltage meets the power requirements of the device.

**Chapter 3**System Setup

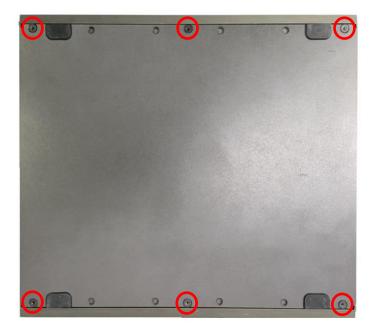

# **3.1 Removing the Top Cover**

WARNING

In order to prevent electric shock or system damage, before removing the chassis cover, must turn off power and disconnect the unit from power source.

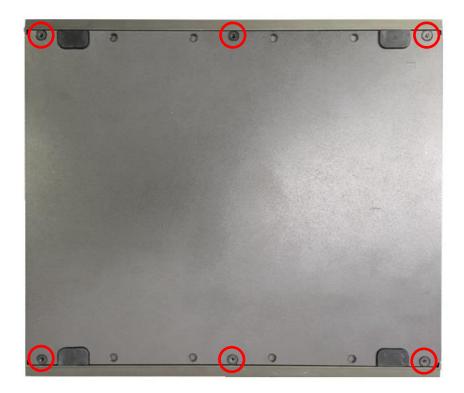

1. Turn over the unit to have the bottom side face up, loosen the 6 screws on the bottom cover and place them aside for later use.

2. Remove the bottom cover from the chassis.

3. Unscrew the 2 screws at rear panel as marked on the photo and place them aside for later use.

4. Loosen the 4 screws. Pull out 4 latches as marked on the photo.

5. Lift up the unit vertically by holding the front and rear panel.

6. Turn over the body of the unit and place it gently.

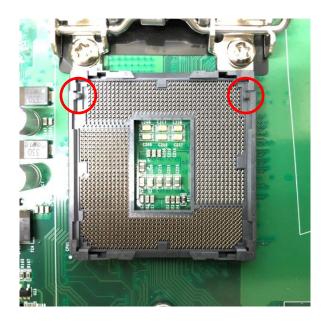

# 3.2 Installing the CPU

1. Locate the CPU socket, remove the protection cover on it.

2. Press the CPU socket lever and pull it aside away from the socket to unlock it. Pull back the lever to open the socket.

3. Align the notches on CPU with the alignment post on socket.

4. The notches of socket provide the space for fingers while lowering the CPU, hold the CPU by the edges toward the notches and insert the CPU gently.

5. Place the thermal pad on the CPU heat spreader. Press down the socket lever to lock the CPU.

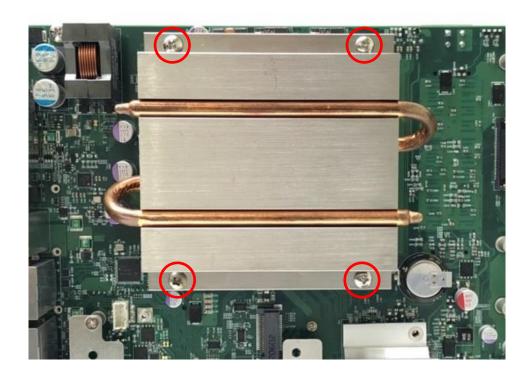

6. Align mounting holes of heatsink with the nut studs and fasten the heat sink with provided 4 screws.

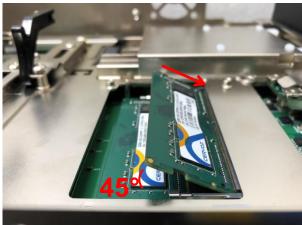

## 3.3 Installing SO-DIMM Memory

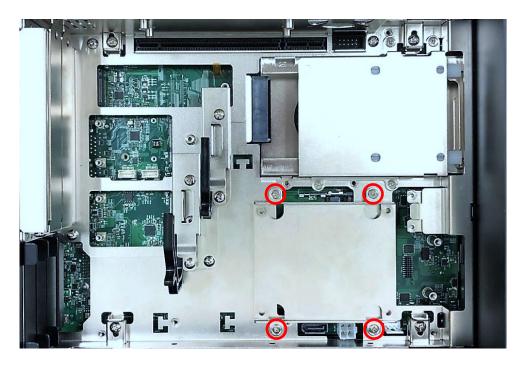

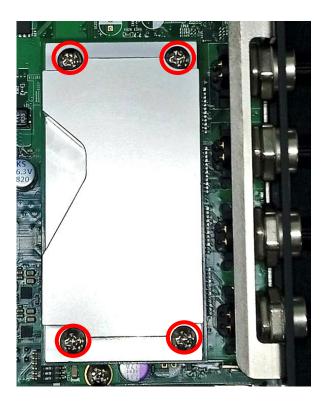

1. Locate the SO-DIMM sockets at the bottom side of system. Unscrews the 4 screws and remove the bracket.

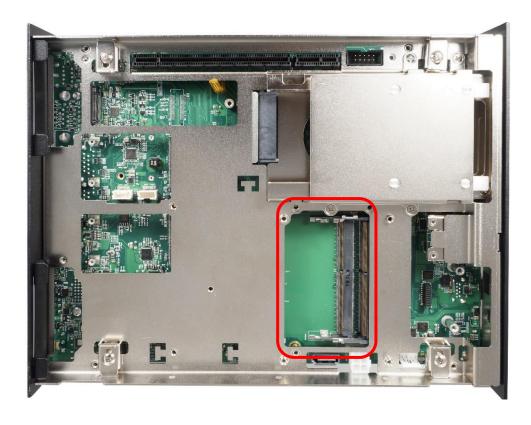

2. Locate two SO-DIMM sockets at the bottom.

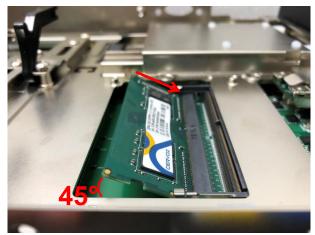

3. Tilt the SO-DIMM module at a 45-degree angle and insert it to SO-DIMM socket until the gold-pated connector of module contacted firmly with the socket.

Lower socket

Upper socket

4. Press the modules down until it's fixed firmly by the two locking latches on the sides.

5. Put the cover back and fix the cover with 4 screws.

## 3.4 Installing a Mini-PCIe/mSATA Card on Top Side

#### (Applicable for full or half size card)

1. Locate the Mini PCIe socket on the top side of system.

2. Use provided two screws fasten the half size module and adapter bracket together as shown in Fig (a) below.

(a) Half Size Mini-PCle Card

(b) Full Size Mini-PCle Card

3. Insert the Mini-PCIe card at a 45-degree angle until its edge connector is connected firmly into slot.

4. Press down the module and fasten two screws to secure the module.

## 3.5 Installing a Mini-PCIe/mSATA Card on Bottom

#### **Side** (Applicable for full or half size card)

1. Turn over the body of the unit. Locate Mini-PCle (mSATA) slots at the bottom.

2. Tilt the Mini-PCIe module at a 45-degree angle and insert it to the slot until the gold-pated connector of module contacted firmly with the slot.

3. Press down the module and use previous two screws to fix the module.

# 3.6 Installing Antennas

1. Remove the antenna rubber covers on rear panel.

2. Have antenna jack penetrate through the hole.

3. Put on washer and fasten the nut with antenna jack.

4. Assemble the antenna and antenna jack together.

5. Attach the RF connector at another end of cable onto the module.

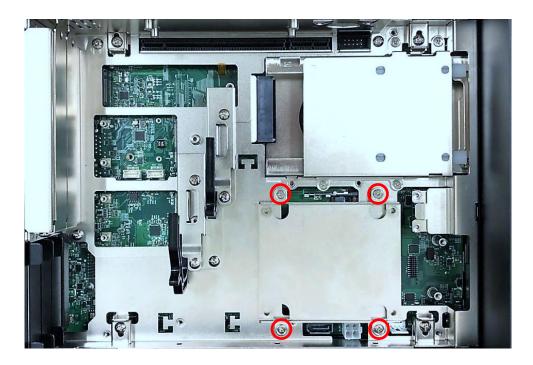

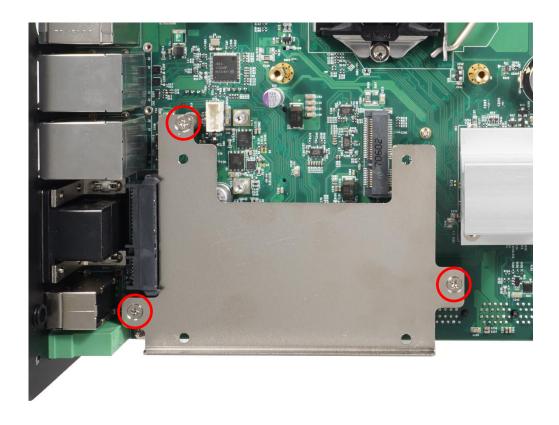

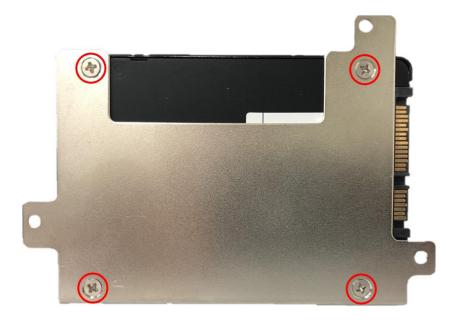

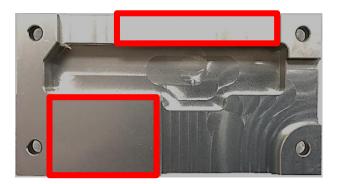

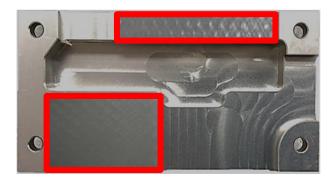

#### 3.7 Installing a SATA Hard Drive on Top Side

1. Unscrew the 3 screws on HDD bracket and remove the bracket.

2. Make the PCB side of the HDD face up, place the HDD bracket on it. Ensure the direction of bracket is correct and use 4 provided screws to assemble HDD and HDD bracket together.

3. Turn over the HDD bracket. Connect the HDD bracket to the SATA connector and fasten the 3 screws.

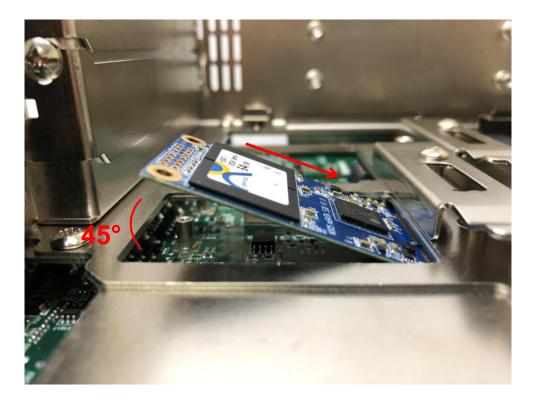

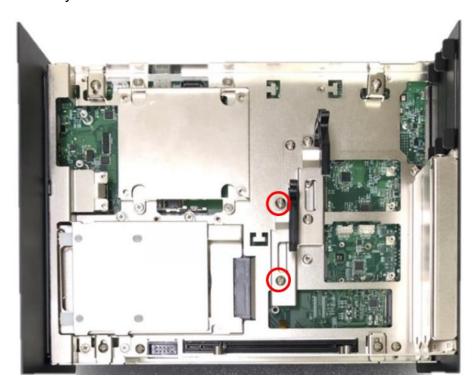

# 3.8 Installing an M.2 Card

1. Turn over the body of the unit. Unscrew the 2 screws and remove the bracket.

2. Locate M.2 slots at the bottom.

3. Tilt the M.2 M Key card at a 45-degree angle and insert it to the slot until the gold-pated connector of module contacted firmly with the slot.

4. Press down the module and use previous one screw to fix the module.

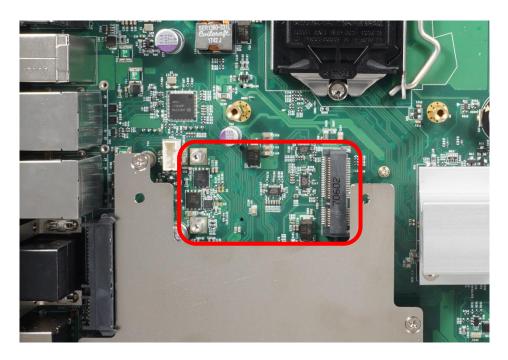

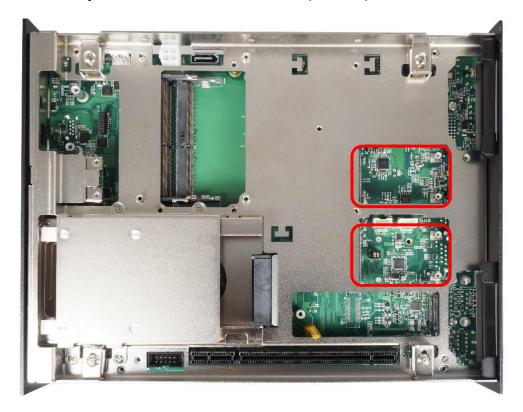

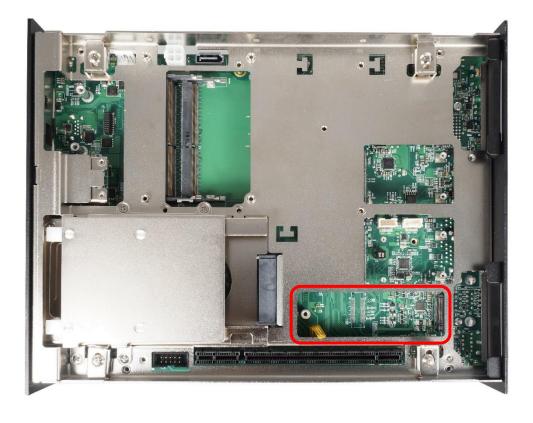

## 3.9 Installing a PCI/PCIe Add-on Card

#### (For DS-1201 and DS-1202 only)

The applicable riser cards for DS-1200 series are listed in the following table.

| Model No.   | Description                        | Compatible Model |

|-------------|------------------------------------|------------------|

| RC-E16-01   | Riser Card 1 x PClex16             | DS-1201          |

| RC-PI-01    | Riser Card 1 x PCI                 | DS-1201          |

| RC-E16E1-01 | Riser Card 1 x PClex16, 1 x PClex1 | DS-1202          |

| RC-E8E8-R10 | Riser Card 2 x PClex8              | DS-1202          |

| RC-E16PI-01 | Riser Card 1 x PClex16, 1 x PCl    | DS-1202          |

| RC-PIPI-01  | Riser Card 2 x PCI                 | DS-1202          |

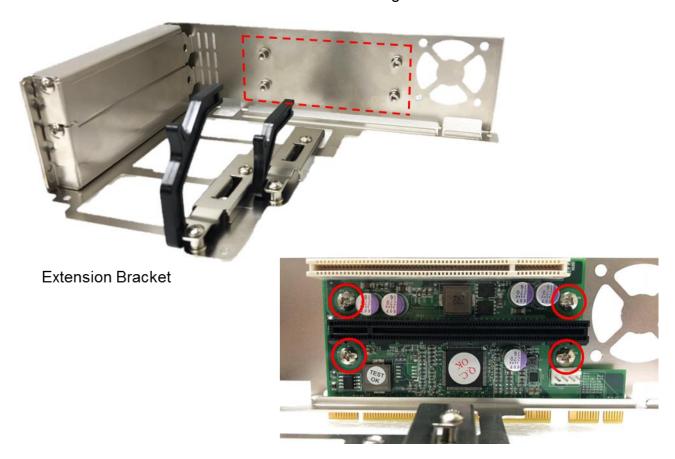

The photo example in this section is illustrated by RC-E16PI-01 module.

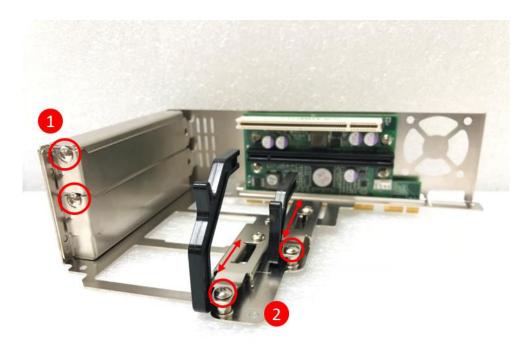

1. Prepare a Riser Card intended for installation.

Riser Card RC-E16PI-01

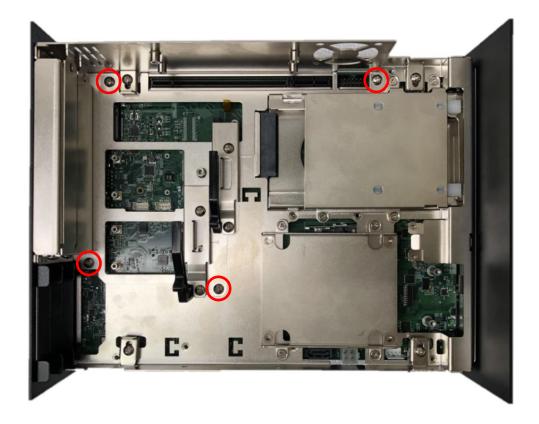

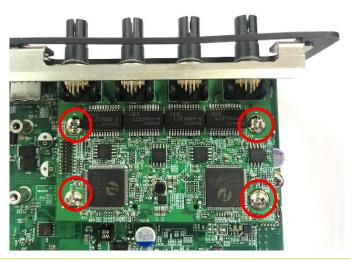

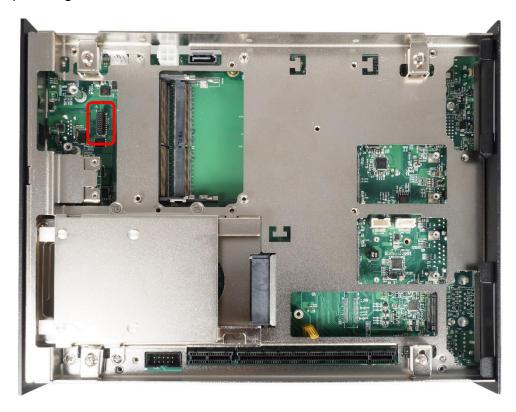

2. Unscrew the 4 screws to remove the extension bracket.

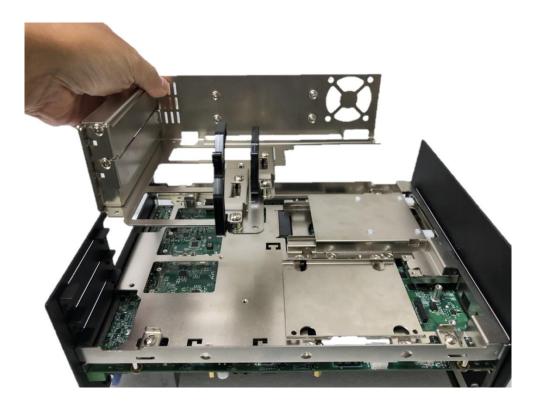

3. Remove the extension bracket from the system.

4. Assemble the riser card with extension bracket together and fasten with the 4 screws.

5. (1) Loosen the screw to remove I/O bracket. (2) Loosen the 2 screws halfway to allow the card retainer to be adjustable.

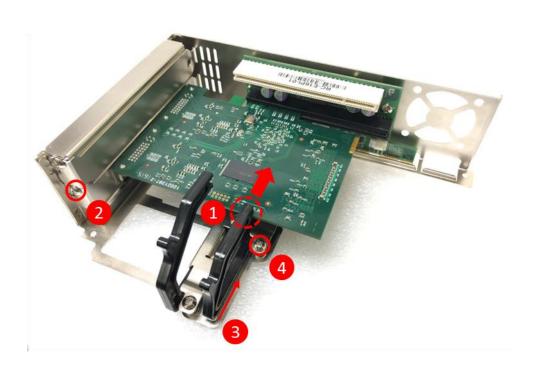

6. (1) Insert a PCI(e) add-on card to the slot. (2) Fasten the screw to secure it (3) Push the card retainer forward to against the edge of the add-on card. (4) Tighten the screw to fix the card retainer.

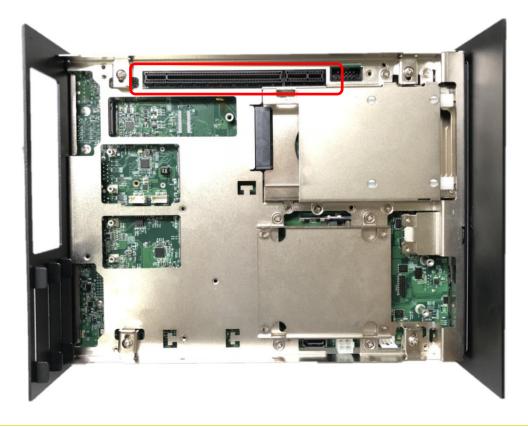

7. Locate the riser card slot on bottom side of system.

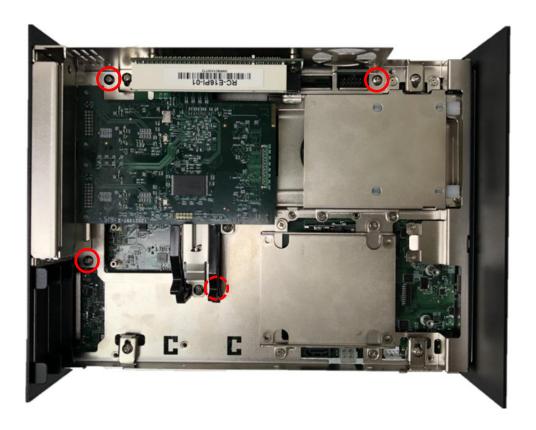

8. Install the module assembled in step 4 into the riser card slot, and fasten the 4 screws to secure it.

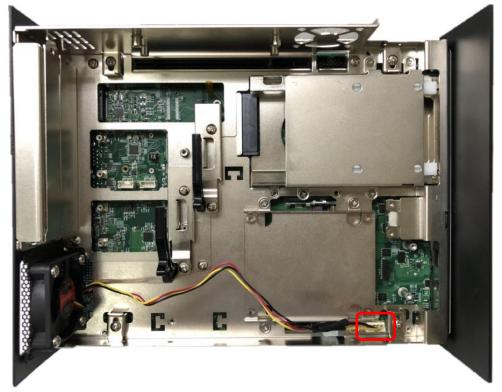

# 3.10 Assembling the System

1. Make sure the notch on chassis and the front bezel of body are at the same side.

2. Lift up the body of unit. Make sure that both front and rear panels are in the chassis groves and assemble the body on to chassis firmly.

3. Push into the 4 latches as indicated and fasten the 4 screws.

4. Fasten the 2 screws at rear panel.

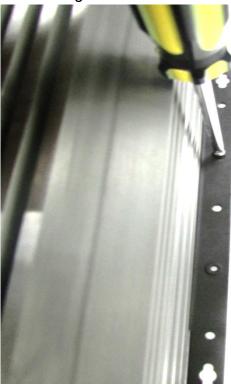

5. Be sure to align the grooves with front and rear panels. Put the cover back on and fasten the 6 screws to fix the cover.

## 3.11 Installing a SATA Hard Drive at Front Side

1. Loosen the screws in order to remove the front expansion plate.

2. Locate the removable HDD bay and loosen the screw.

3. Move the rotating arm out and pull the HDD bracket out.

4. Make the PCB side of the HDD face up, place the HDD bracket into it. Ensure the direction of bracket is correct and use 4 provided screws to assemble HDD and HDD bracket together.

5. Align the HDD bracket with the entrance of HDD bay. Holding the rotating arm and insert the HDD bracket until the connector of HDD contact the SATA connector firmly.

6. Place the rotating arm back and fasten the screw.

# 3.12 Installing a SIM Card

1. Locate the SIM card slot at front side.

2. Insert the SIM card according to the icon instruction aside.

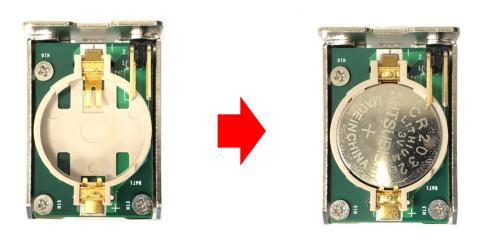

## **3.13 Installing the CMOS Battery**

1. Locate the removable CMOS Battery and loosen the screw.

2. Pull out the CMOS battery bracket with assistance of a tweezer.

3. Insert a CMOS battery in the battery slot.

4. Insert the battery bracket firmly and fasten the screw.

# **3.14 Fastening the Cover**

1. Fasten the cover by using the two screws.

#### 3.15 Wall Mount Brackets

DS-1200 series offers wall mount that customers can install system on the wall in convenient and economical ways.

1. The mounting holes are at the bottom side of the system. Use the provided 8 screws to fasten the bracket and the system together.

2. Fasten the screws through the bracket mounting hole to mount system on the wall.

# **Chapter 4**BIOS Setup

#### 4.1 BIOS Introduction

The BIOS (Basic Input/ Output System) is a program located on a Flash Memory on the motherboard. When you start the computer, the BIOS program will gain control. The BIOS first operates an auto-diagnostic test called POST (power on self-test) for all the necessary hardware, it detects the entire hardware device and configures the parameters of the hardware synchronization.

#### **BIOS Setup**

Power on the computer and by pressing <Del> immediately allows you to enter Setup. If the message disappears before your respond and you still wish to enter Setup, restart the system to try again by turning it OFF then ON or pressing <Ctrl>, <Alt> and <Delete> keys.

| Control Keys               |                                              |  |

|----------------------------|----------------------------------------------|--|

| <->>                       | Move to select screen                        |  |

| <↑> <↓>                    | Move to select item                          |  |

| <esc></esc>                | Quit the BIOS Setup                          |  |

| <enter></enter>            | Select item                                  |  |

| <page +="" up=""></page>   | Increases the numeric value or makes changes |  |

| <page -="" down=""></page> | Decreases the numeric value or makes changes |  |

| <tab></tab>                | Select setup fields                          |  |

| <f1></f1>                  | General help                                 |  |

| <f2></f2>                  | Previous value                               |  |

| <f3></f3>                  | Load Optimized defaults                      |  |

| <f10></f10>                | Save configuration and Exit                  |  |

#### Main Menu

The main menu lists the setup functions you can make changes to. You can use the arrow keys (  $\uparrow\downarrow$  ) to select the item. The on-line description of the highlighted setup function is displayed at the bottom of the screen.

#### Sub-Menu

If you find a right pointer symbol appears to the left of certain fields that means a sub-menu can be launched from this field. A sub-menu contains additional options for a field parameter. You can use arrow keys (  $\uparrow\downarrow$  ) to highlight the field and press <Enter> to call up the sub-menu. Then you can use the control keys to enter values and move from field to field within a sub-menu. If you want to return to the main menu, just press the <Esc>.

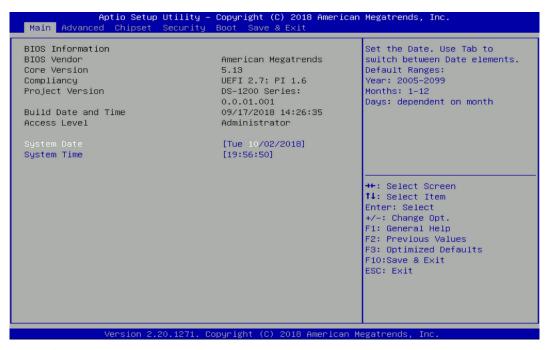

#### 4.2 Main Setup

Press <Del> to enter BIOS CMOS Setup Utility, the Main Menu (as shown below) will appears on the screen. Use arrow keys to move among the items and press <Enter> to accept or enter a sub-menu.

#### 4.2.1 System Date

Set the date. Please use <Tab> to switch between date elements.

#### 4.2.2 System Time

Set the time. Please use <Tab> to switch between time elements.

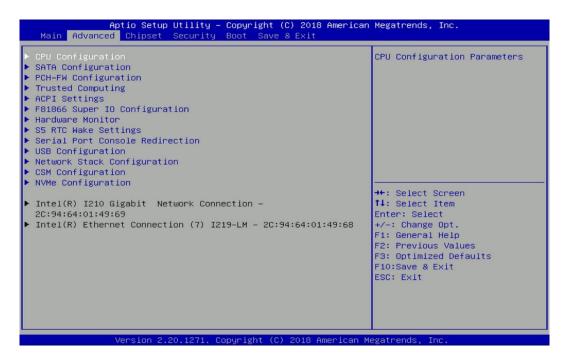

# 4.3 Advanced Setup

This section allows you to configure and improve your system and allows you to set up some system features according to your preference.

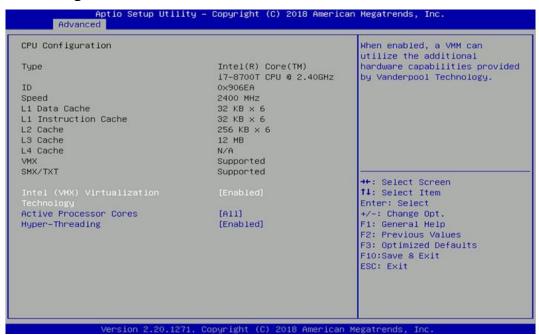

#### 4.3.1 CPU Configuration

#### Intel (VMX) Virtualization Technology [Enabled]

Enables or disables Intel (VMX) Virtualization Technology. Virtualization enhanced by Intel Virtualization Technology will allow a platform to run multiple operating systems and applications in independent partitions. With virtualization, one computer system can function as multiple virtual systems.

#### ■ Active Process Cores [All]

Allows you to choose the number of active processor cores.

Configuration options: [All] [1].

#### Hyper-threading

Enables or disables for Hyper-Threading Technology.

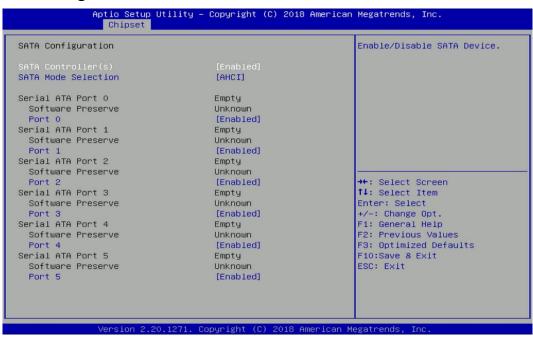

#### 4.3.2 SATA Configuration

#### ■ SATA Controller(s) [Enabled]

Enables or disables SATA device.

#### ■ SATA Mode Selection [AHCI]

Allows you to select which mode SATA controller will operates.

Configuration options: [AHCI], [RAID]

- Serial ATA Port 0

- □ Port 0 [Enabled]

Enables or disables SATA Port 0.

- Serial ATA Port 1

- □ Port 1 [Enabled]

Enables or disables SATA Port 1.

- Serial ATA Port 2

- □ Port 2 [Enabled]

Enables or disables SATA Port 2.

- Serial ATA Port 3

- □ Port 3 [Enabled]

Enables or disables SATA Port 3.

- Serial ATA Port 4

- □ Port 4 [Enabled]

Enables or disables SATA Port 4.

- Serial ATA Port 5

- □ Port 5 [Enabled]

Enables or disables SATA Port 5.

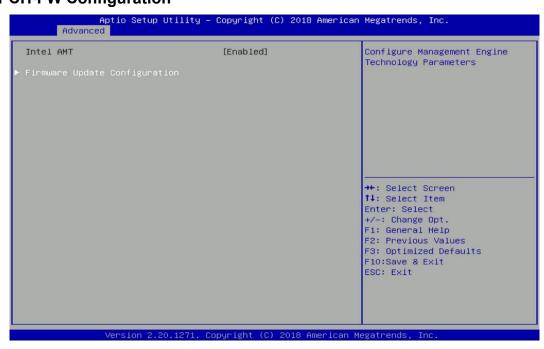

#### 4.3.3 PCH-FW Configuration

#### Firmware Update Configuration

Configure Management Engine Parameters

■ Me FW Image Re-Flash [Disabled]

Enables or disables Me FW Image Re-Flash function.

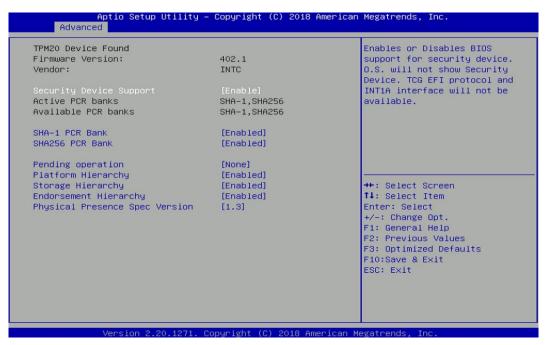

#### 4.3.4 Trusted Computing

#### Security Device Support [Enabled]

Enables or disables BIOS support for security device.

#### ■ SHA-1 PCR Bank [Enabled]

Enables or disables SHA-1 PCR (Platform Configuration Register) Bank.

#### ■ SHA256 PCR Bank [Enabled]

Enables or disables SHA256 PCR (Platform Configuration Register) Bank.

#### Pending operation [None]

Schedule an Operation for the security device.

[None]: No operation.

[TPM Clear]: Clear TPM status.

#### ■ Platform Hierarchy [Enabled]

Enables or disables platform hierarchy.

#### ■ Storage Hierarchy [Enabled]

Enables or disables storage hierarchy.

#### **■** Endorsement Hierarchy [Enabled]

Enables or disables endorsement hierarchy.

#### ■ Physical Presence Spec Version [1.3]

Select the physical presence spec version.

Configuration options: [1.2] [1.3]

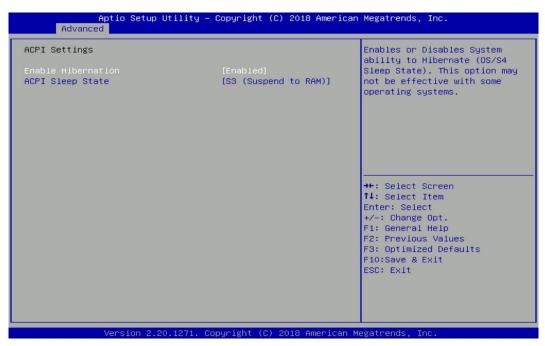

#### 4.3.5 ACPI Settings

#### ■ Enable Hibernation [Enabled]

Enables or disables system ability to hibernate state (OS/S4 state). This option may not be effective with some OS.

#### ■ ACPI Sleep State [S3 (Suspend to RAM)]

Allows users to select the highest Advanced Configuration Power Interface® (ACPI) sleep state that system will enter when suspend button is pressed.

[Suspend Disabled]: Disables entering suspend state.

[S3 (suspend to RAM)]: Enables suspend to RAM state.

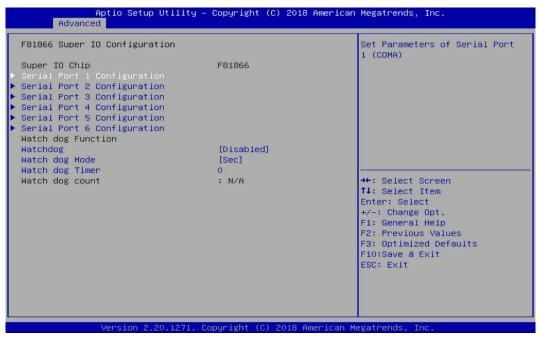

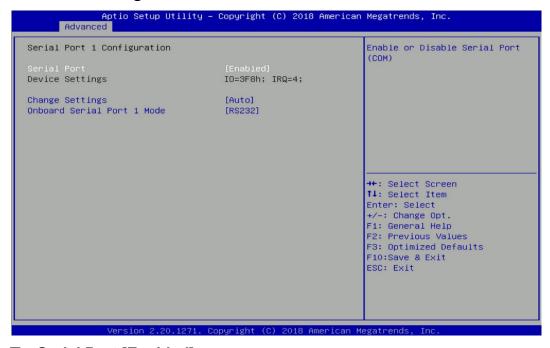

#### 4.3.6 F81866 Super IO Configuration

Set Parameters of Serial Ports. User can Enable/Disable the serial port and Select an optimal setting for the Super IO Device.

#### ■ Serial Port 1~6 Configuration.

#### □ Serial Port [Enabled]

Enables or disables serial port.

#### □ Change Settings [Auto]

Allows you to change the IO Address & IRQ settings of the specified serial port.

#### □ Onboard Serial Port 1~6 Mode [RS232]

Allows you to select Serial Port Mode.

Configuration options: [RS232] [RS422/RS485 Full Duplex] [RS485 Half Duplex]

#### Watch Dog [Disabled]

Enables or disables watch dog function.

#### Watch Dog Mode [Sec]

Allows to set watchdog timer unit <Sec> or <Min>.

#### ■ Watch Dog Timer [0]

Allows you to set watchdog timer's value in the range of 0 to 255.

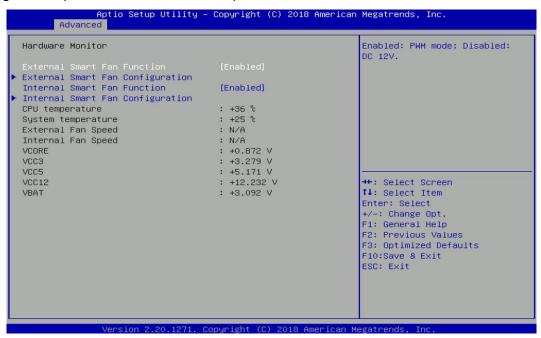

#### 4.3.7 Hardware Monitor

This screen displays the current status of all monitored hardware devices/components such as voltages, temperatures and all fans' speeds.

#### External Smart Fan Function [Enabled]

Enables or disables external smart fan function.

#### ■ External Smart Fan Configuration

Allows users to setting external smart fan parameters.

#### Internal Smart Fan Function [Enabled]

Enables or disables internal smart fan function.

#### Internal Smart Fan Configuration

Allows users to setting internal smart fan parameters.

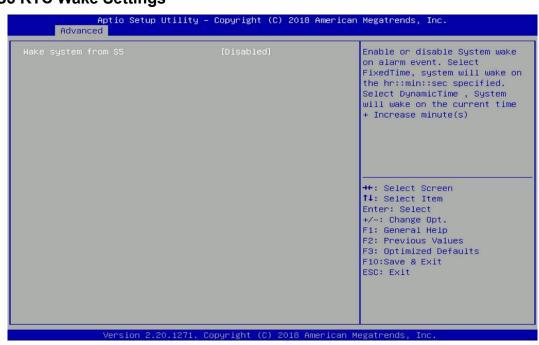

#### 4.3.8 S5 RTC Wake Settings

#### Wake system from S5 [Disabled]

Enables or disables wake system from S5 (soft-off state).

[Disabled]: Disables wake system from S5.

[Fixed Time]: Sets a fixed time (HH:MM:SS) to wake system from S5.

[Dynamic Time]: Sets an increase minute(s) from current time to wake system from S5.

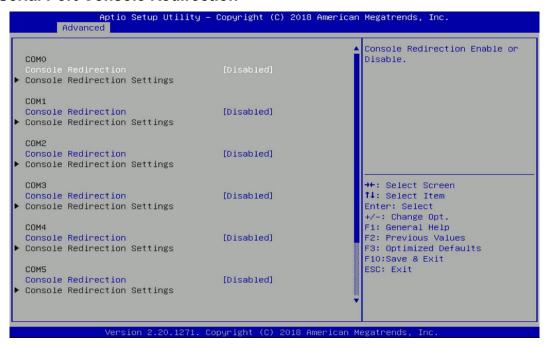

#### 4.3.9 Serial Port Console Redirection

#### Console Redirection

Allow users to enable or disable COM0, COM1, COM2, COM3, COM4, COM5 console redirection function.

COM0 = Serial Port 1

COM1 = Serial Port 2

COM2 = Serial Port 3

COM3 = Serial Port 4

COM4 = Serial Port 5

COM5 = Serial Port 6

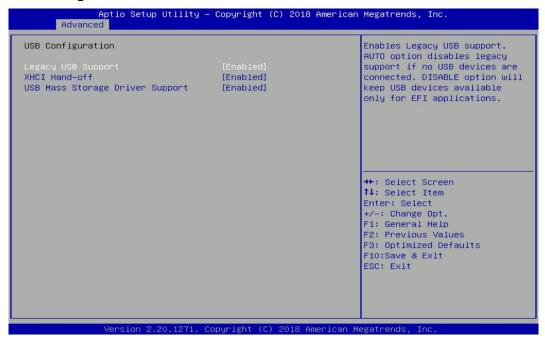

#### 4.3.10 USB Configuration

#### ■ Legacy USB Support [Enabled]

This item allows users to enable or disable legacy USB support. When set to [Auto], legacy USB support will be disabled automatically if no USB devices are connected.

#### **■** XHCI Hand-off [Enabled]

Enables or disables XHCI (USB3.0) hand-off function. Use this feature as a workaround for operating systems without XHCI hand-off support.

#### ■ USB Mass Storage Driver Support [Enabled]

Enables or disables USB mass storage driver support.

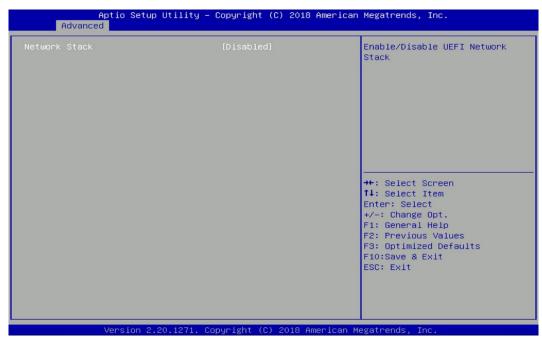

#### 4.3.11 Network Stack Configuration

#### ■ Network Stack [Disabled]

Enables or disables UEFI Network Stack.

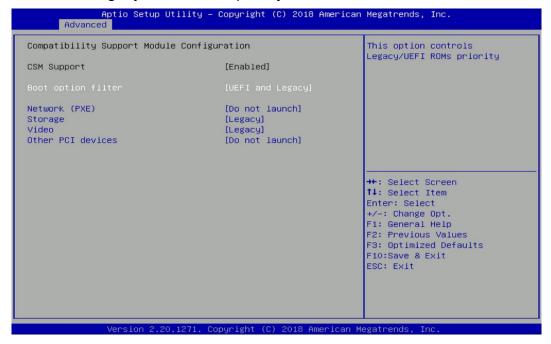

#### 4.3.12 CSM Configuration

This option controls legacy/UEFI ROMs priority.

#### Boot option filter [UEFI and Legacy]

Allows you to select which type of operating system to boot.

[UEFI and Legacy]: Allows booting from operating systems that support legacy option ROM or UEFI option ROM.

[Legacy only]: Allows booting from operating systems that only support legacy option ROM. [UEFI only]: Allows booting from operating systems that only support UEFI option ROM.

#### Network PXE [Do not launch]

Controls the execution of UEFI and Legacy PXE (Network Preboot eXecution Environment) option ROM.

[Do not launch]: Disables option ROM execution.

[Legacy]: Enables legacy option ROM only.

#### ■ Storage [Legacy]

Controls the execution of UEFI and Legacy Storage option ROM.

[Do not launch]: Disables option ROM execution.

[UEFI]: Enables UEFI option ROM only.

[Legacy]: Enables legacy option ROM only.

#### ■ Video [Legacy]

Controls the execution of UEFI and Legacy Video option ROM.

[Do not launch]: Disables option ROM execution.

[UEFI]: Enables UEFI option ROM only.

[Legacy]: Enables legacy option ROM only.

#### ■ Other PCI devices [Do not launch]

Allows users to determine option ROM execution policy for devise other than network, storage, or video.

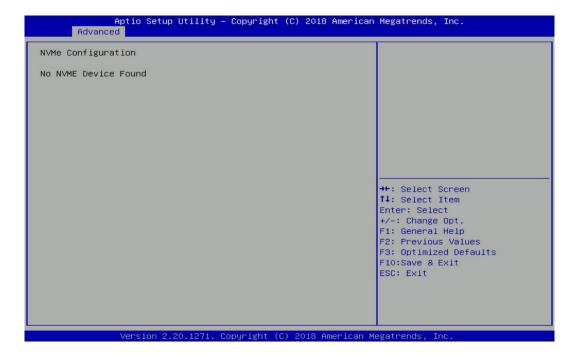

#### 4.3.13 NVMe Configuration

This screen displays the current NVMe device information.

# 4.4 Chipset Setup

This section allows you to configure chipset related settings according to user's preference.

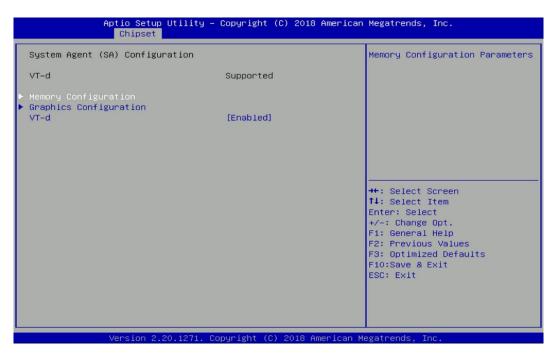

#### 4.4.1 System Agent (SA) Configuration

#### Memory Configuration

This item displays detailed memory configuration in the system.

#### ■ Max TOLUD [Dynamic]

This feature sets the maximum TOLUD (Top of Low Usable DRAM) value, which specifies the TOLUD memory space to be used by internal graphics devices, GTT Stolen Memory, and TSEG, respectively, if these devices are enabled.

Configuration options: [Dynamic] [1 GB] [1.25 GB] [1.5 GB] [1.75 GB] [2 GB] [2.25 GB] [2.5 GB] [2.75 GB] [3 GB]

#### ■ Graphics Configuration

#### Primary Display [Auto]

Allows users to select which graphics device should be primary display or select SG for switchable graphics.

Configuration options: [Auto] [IGFX] [PEG] [PCIe]

#### □ Internal Graphics [Auto]

Allows users to enable or disable Internal Graphics.

Configuration options: [Auto] [Disabled] [Enabled]

#### ■ VT-d [Enabled]

Enables or disables Intel® Virtualization Technology for Directed I/O (VT-d) capability.

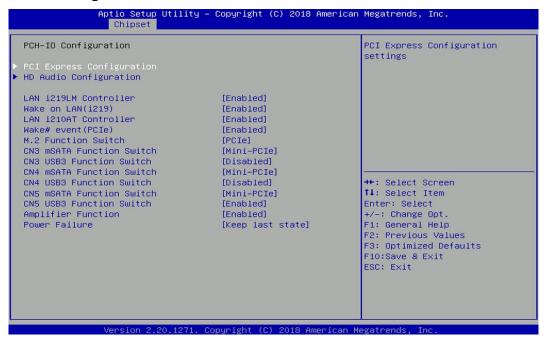

#### 4.4.2 PCH-IO Configuration

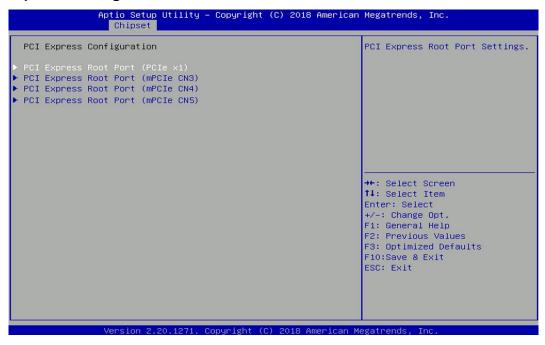

#### PCI Express Configuration

#### PCI Express Root Port (PCIe x1)

□ PCI Express Root Port 1 [Enabled]

Enables or disables PCI Express Root Port 1.

□ PCIeSpeed [Auto]

Allows you to select PCI Express port speed.

Configuration options: [Auto] [Gen1] [Gen2] [Gen3].

#### **PCI Express Root Port (mPCIe CN3)**

□ PCI Express Root Port 1 [Enabled]

Enables or disables PCI Express Root Port 1.

□ PCIeSpeed [Auto]

Allows you to select PCI Express port speed.

Configuration options: [Auto] [Gen1] [Gen2] [Gen3].

#### PCI Express Root Port (mPCle CN4)

□ PCI Express Root Port 1 [Enabled]

Enables or disables PCI Express Root Port 1.

□ PCIeSpeed [Auto]

Allows you to select PCI Express port speed.

Configuration options: [Auto] [Gen1] [Gen2] [Gen3].

#### **PCI Express Root Port (mPCIe CN5)**

□ PCI Express Root Port 1 [Enabled]

Enables or disables PCI Express Root Port 1.

□ PCIeSpeed [Auto]

Allows you to select PCI Express port speed.

Configuration options: [Auto] [Gen1] [Gen2] [Gen3].

#### ■ LAN i219LM Controller [Enabled]

Enables or disables I219LM LAN Controller.

#### ■ Wake on LAN (i219) [Enabled]

Enables or disables integrated LAN i219LM Wake On LAN function.

#### LAN i210AT Controller [Enabled]

Enables or disables I210 LAN Controller.

#### ■ Wake# event (PCle) [Enabled]

Enables or disables integrated LAN I210 Wake On LAN function.

#### ■ M.2 function Switch [PCle]

Select PCIe/SATA for M.2 connector.

#### ■ CN3 mSATA Function Switch [Mini-PCle]

Allows you to change Mini PCle1 (CN3) as [Mini-PCle] or [mSATA].

#### ■ CN3 USB3 Function Switch [Disabled]

Enables or disables CN3 USB3 Controller.

#### ■ CN4 mSATA Function Switch [Mini-PCle]

Allows you to change Mini PCle1 (CN4) as [Mini-PCle] or [mSATA].

#### CN4 USB3 Function Switch [Disabled]

Enables or disables CN4 USB3 Controller.

#### ■ CN5 mSATA Function Switch [Mini-PCle]

Allows you to change Mini PCle1 (CN5) as [Mini-PCle] or [mSATA].

#### ■ CN5 USB3 Function Switch [Disabled]

Enables or disables CN5 USB3 Controller.

#### ■ Amplifier Function [Enabled]

Enables or disables Amplifier Function.

#### ■ Power Failure [Keep last state]

Allows you to specify which power state system will enter when power is resumed after a power failure (G3 state).

[Always on]: Enters to power on state.

[Always off]: Enters to power off state.

[Keep last state]: Enters to the last power state before a power failure.

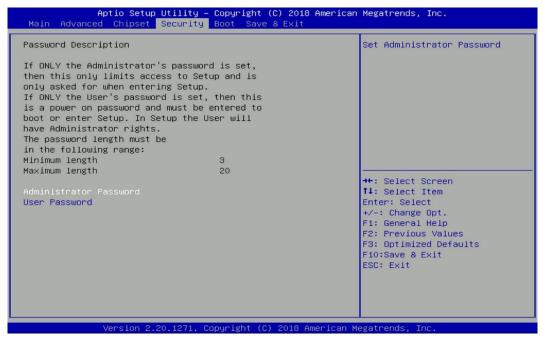

# 4.5 Security Setup

This section allows users to configure BIOS security settings.

#### 4.5.1 Administrator Password

Administrator Password controls access to the BIOS Setup utility.

#### 4.5.2 User Password

User Password controls access to the system at boot and to the BIOS Setup utility.

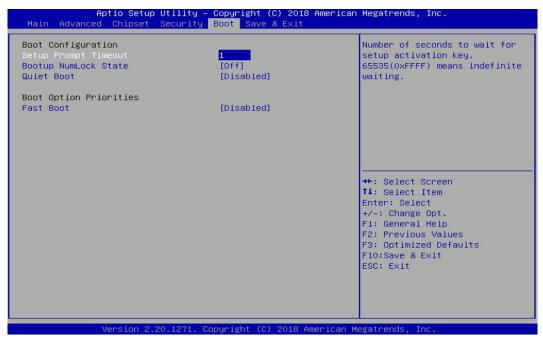

# 4.6 Boot Setup

This section allows you to configure Boot settings.

#### Setup Prompt Timeout [1]

Use this item to set number of seconds (1..65535) to wait for setup activation key.

#### Bootup NumLock State

Allows you to set NumLock key to [On] or [Off] state when system boots up.

#### Quiet Boot

Allows you to enable or disable Quiet Boot function.

#### ■ Fast Boot

Allows you to enable or disable Fast Boot function. If enabled, system boots with initialization of a minimal set of devices required to launch active boot option.

#### ■ Hard Drive BBS Priority

Allows you to set the order of the legacy devices in this group.

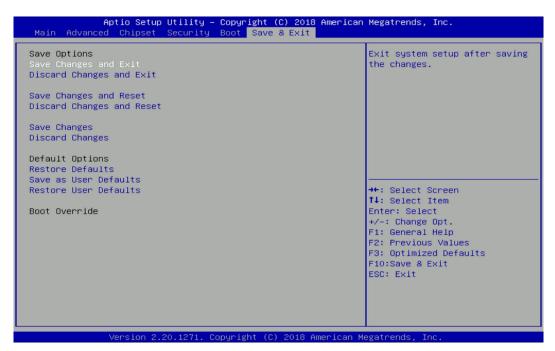

#### 4.7 Save & Exit

#### Save Changes and Exit

This item allows you to exit the system after saving changes.

#### ■ Discard Changes and Exit

This item allows you to reset the system setup without saving any changes.

#### ■ Save Changes and Reset

This item allows you to reset the system after saving changes.

#### Discard Changes and Reset

This item allows you to reset the system setup without saving any changes.

#### Save Changes

This item allows you to save changes done so far to any of the setup options.

#### Discard Changes

This item allows you to discard changes done so far to any of the setup options.

#### ■ Restore Defaults

This item allows you to restore/ load default values for all the setup options.

#### Save as User Defaults

This item allows you to save the changes done so far as user defaults.

#### ■ Restore User Defaults

This item allows you to restore the user defaults to all the setup options.

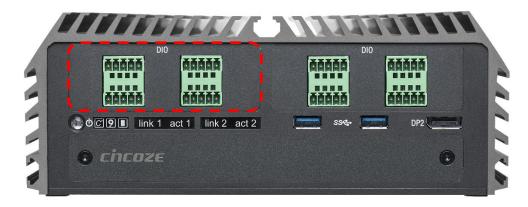

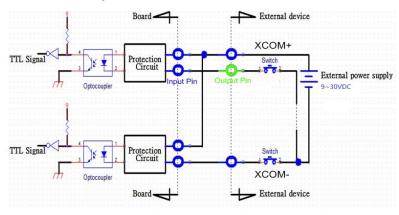

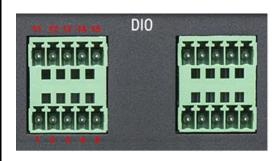

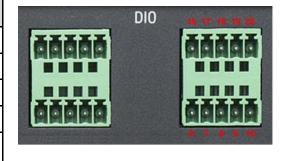

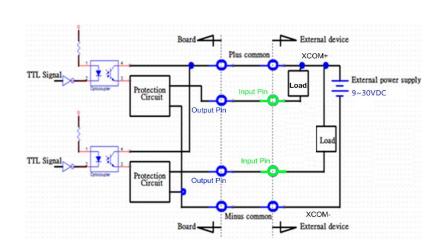

# Chapter 5 Product Application (For DIO only)

# 5.1 Digital I/O (DIO) application

This section describes DIO application of the product. The content and application development are better understood and implemented by well experienced professionals or developers.

## 5.1.1 Digital I/O Programming Guide

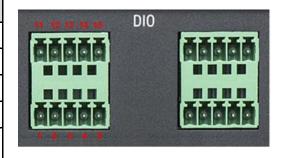

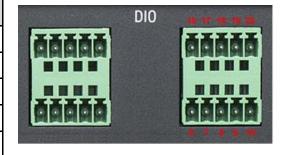

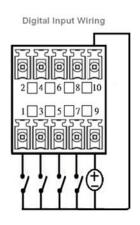

#### 5.1.1.1 Pins for Digital I/O 1~8

| Item             | Standard | Item             | Standard |

|------------------|----------|------------------|----------|

| GPIO70 (PIN 103) | DI       | GPIO80 (PIN 111) | DO       |

| GPIO71 (PIN 104) |          | GPIO81 (PIN 112) |          |

| GPIO72 (PIN 105) |          | GPIO82 (PIN 113) |          |

| GPIO73 (PIN 106) |          | GPIO83 (PIN 114) |          |

| GPIO74 (PIN 107) |          | GPIO84 (PIN 115) |          |

| GPIO75 (PIN 108) |          | GPIO85 (PIN 116) |          |

| GPIO76 (PIN 109) |          | GPIO86 (PIN 117) |          |

| GPIO77 (PIN 110) |          | GPIO87 (PIN 118) |          |

#### 5.1.1.2 Pins for Digital I/O 9-16

| Item            | Standard | Item            | Standard |

|-----------------|----------|-----------------|----------|

| GPIO30 (PIN 36) | DI       | GPIO40 (PIN 44) | DO       |

| GPIO31 (PIN 37) |          | GPIO41 (PIN 45) |          |

| GPIO32 (PIN 38) |          | GPIO42 (PIN 46) |          |

| GPIO33 (PIN 39) |          | GPIO43 (PIN 47) |          |

| GPIO34 (PIN 40) |          | GPIO44 (PIN 48) |          |

| GPIO35 (PIN 41) |          | GPIO45 (PIN 49) |          |

| GPIO36 (PIN 42) |          | GPIO46 (PIN 50) |          |

| GPIO37 (PIN 43) |          | GPIO47 (PIN 51) |          |

#### 5.1.1.3 Programming Guide

To program the Super I/O chip F81866A configuration registers, the following configuration procedures must be followed in sequence:

- (1) Enter the Extended Function Mode

- (2) Configure the configuration registers

- (3) Exit the Extended Function Mode

The configuration register is used to control the behavior of the corresponding devices. To configure the register, use the index port to select the index and then write data port to alter the parameters. The default index port and data port are 0x4E and 0x4F, respectively.

Pull down the SOUT1 pin to change the default value to 0x2E/ 0x2F. To enable configuration, the entry key 0x87 must be written to the index port. To disable configuration, write exit entry key 0xAA to the index port.

Following is an example to enable configuration and to disable configuration by using debug.

- -o 4e 87

- -o 4e 87 (enable configuration)

- -o 4e aa (disable configuration)

#### 5.1.1.4 Relative Registers

To program the F81866A configuration registers, see the following configuration procedures.

Logic Device Number Register (LDN) — Index 07h

| Bit | Name | R/W | Reset   | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------|-----|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | LDN  | R/W | LRESET# |         | 00h: Select FDC device configuration registers. 03h: Select Parallel Port device configuration registers. 04h: Select Hardware Monitor device configuration registers. 05h: Select KBC device configuration registers. 06h: Select GPIO device configuration registers. 07h: Select WDT device configuration registers. 07h: Select PME, ACPI and ERP device configuration registers. 10h: Select UART1 device configuration registers. 11h: Select UART2 device configuration registers. 12h: Select UART3 device configuration registers. 13h: Select UART4 device configuration registers. 14h: Select UART5 device configuration registers. 15h: Select UART6 device configuration registers. Otherwise: Reserved. |

#### 8.7.13.1GPIO7 Output Enable Register — Index 80h

| Bit | Name      | R/W | Reset   | Default | Description                                                 |

|-----|-----------|-----|---------|---------|-------------------------------------------------------------|

| 7   | GPIO77_OE | R/W | LRESET# | 0       | 0: GPIO77 is in input mode.<br>1: GPIO77 is in output mode. |

| 6   | GPIO76_OE | R/W | LRESET# | 0       | 0: GPIO76 is in input mode.<br>1: GPIO75 is in output mode. |

| 5   | GPIO75_OE | R/W | LRESET# | 0       | 0: GPIO75 is in input mode.<br>1: GPIO75 is in output mode. |

| 4   | GPIO74_OE | R/W | LRESET# | 0       | 0: GPIO74 is in input mode.<br>1: GPIO74 is in output mode. |

| 3   | GPIO73_OE | R/W | LRESET# | 0       | 0: GPIO73 is in input mode.<br>1: GPIO73 is in output mode. |

| 2   | GPIO72_OE | R/W | LRESET# | 0       | 0: GPIO72 is in input mode.<br>1: GPIO72 is in output mode. |

| 1   | GPIO71_OE | R/W | LRESET# | 0       | 0: GPIO71 is in input mode.<br>1: GPIO71 is in output mode. |

| 0   | GPIO70_OE | R/W | LRESET# | 0       | 0: GPIO70 is in input mode.<br>1: GPIO70 is in output mode. |

#### 8.7.13.3GPIO7 Pin Status Register — Index 82h (This byte could be also read by base address + 3)

| Bit | Name      | R/W | Reset | Default | Description                                   |

|-----|-----------|-----|-------|---------|-----------------------------------------------|

| 7   | GPIO77_IN | R   | -     | -       | The pin status of GPIO77/STB#.                |

| 6   | GPIO76_IN | R   | -     | -       | The pin status of GPIO76/AFD#.                |

| 5   | GPIO75_IN | R   | -     | -       | The pin status of GPIO75/ERR#.                |

| 4   | GPIO74_IN | R   | -     | -       | The pin status of GPIO74/INIT#.               |

| 3   | GPIO73_IN | R   | -     | -       | The pin status of GPIO73/SLIN#.               |

| 2   | GPIO72_IN | R   | -     | -       | The pin status of GPIO72/ACK#.                |

| 1   | GPIO71_IN | R   | -     | -       | The pin status of GPIO71/BUSY.                |

| 0   | GPIO70_IN | R   | -     | -       | The pin status of GPIO70/PE/FANCTL3/PWM_DAC3. |

#### 8.7.9.1 GPIO3 Output Enable Register — Index C0h

|     | et les eupat Eliano l'organis l'index est |      |           |         |                      |  |  |  |  |

|-----|-------------------------------------------|------|-----------|---------|----------------------|--|--|--|--|

| Bit | Name                                      | R/W  | Reset     | Default | Description          |  |  |  |  |

| 7   | GPIO37_OE                                 | R/W  | LRESET#   | 0       | 0: GPIO37 is input.  |  |  |  |  |

| _ ' | GF1037_OE                                 | 1000 | LKESE1#   | Ů       | 1: GPIO37 is output. |  |  |  |  |

| 6   | GPIO36_OE                                 | R/W  | LRESET#   | 0       | 0: GPIO36 is input.  |  |  |  |  |

| Ľ   | GF1030_OE                                 | 1000 | LKESE1#   |         | 1: GPIO36 is output. |  |  |  |  |

| 5   | GPIO35 OE                                 | R/W  | LRESET#   | 0       | 0: GPIO35 is input.  |  |  |  |  |

| Ľ   | GF1035_OL                                 | 1000 | LKESE1#   | Ů       | 1: GPIO35 is output. |  |  |  |  |

| 4   | GPIO34 OE                                 | R/W  | LRESET#   | # O     | 0: GPIO34 is input.  |  |  |  |  |

| Ľ   | 011034_01                                 | 1000 | LKESE1#   |         | 1: GPIO34 is output. |  |  |  |  |

| 3   | GPIO33_OE                                 | R/W  | V LRESET# | 0       | 0: GPIO33 is input.  |  |  |  |  |

| Ľ   | 011000_02                                 | 1000 | ERESE1#   |         | 1: GPIO33 is output. |  |  |  |  |

| 2   | GPIO32 OE                                 | R/W  | LRESET#   | 0       | 0: GPIO32 is input.  |  |  |  |  |

|     | 011032_01                                 | 1000 | LKL3L1#   | Ů       | 1: GPIO32 is output. |  |  |  |  |

| 1   | GPIO31 OE                                 | R/W  | LRESET#   | 0       | 0: GPIO31 is input.  |  |  |  |  |

|     | GF1031_0E                                 | 1000 | LKESET#   |         | 1: GPIO31 is output. |  |  |  |  |

| 0   | GPIO30_OE                                 | R/W  | LRESET#   | 0       | 0: GPIO30 is input.  |  |  |  |  |