# **User Manual**

# iDAQ Chassis (iDAQ-934 & iDAQ-964)

# Copyright

The documentation and the software included with this product are copyrighted 2021 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated, or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. The information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties that may result from its use.

## **Acknowledgments**

Intel and Pentium are trademarks of Intel Corporation.

Microsoft Windows and MS-DOS are registered trademarks of Microsoft Corp. All other product names or trademarks are properties of their respective owners.

# **Product Warranty (2 years)**

Advantech warrants the original purchaser that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products that have been repaired or altered by persons other than repair personnel authorized by Advantech, or products that have been subject to misuse, abuse, accident, or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced free of charge during the warranty period. For out-of-warranty repairs, customers will be billed according to the cost of replacement mate-rials, service time, and freight. Please consult your dealer for more details.

If you believe your product to be defective, follow the steps outlined below.

- 1. Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages displayed when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain a return merchandise authorization (RMA) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a completed Repair and Replacement Order Card, and a proof of purchase date (such as a photocopy of your sales receipt) into a shippable container. Products returned without a proof of purchase date are not eligible for warranty service.

- 5. Write the RMA number clearly on the outside of the package and ship the package prepaid to your dealer.

Part No. 2001093400 Printed in Taiwan

# **Declaration of Conformity**

#### CE

This product has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This type of cable is available from Advantech. Please contact your local supplier for ordering information.

Test conditions for passing also include the equipment being operated within an industrial enclosure. In order to protect the product from damage caused by electrostatic discharge (ESD) and EMI leakage, we strongly recommend the use of CEcompliant industrial enclosure products.

#### FCC Class A

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference. In this event, users are required to correct the interference at their own expense.

### **Technical Support and Assistance**

- 1. Visit the Advantech website at www.advantech.com/support to obtain the latest product information.

- 2. Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Please have the following information ready before calling:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

## Warnings, Cautions, and Notes

Warning! Warnings indicate conditions that if not observed can cause personal injury!

**Caution!** Cautions are included to help prevent hardware damage and data losses. For example,

"Batteries are at risk of exploding if incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type as recommended by the manufacturer.

Discard used batteries according to the manufacturer's instructions."

Notes provide additional optional information.

## **Document Feedback**

To assist us with improving this manual, we welcome all comments and constructive criticism. Please send all feedback in writing to support@advantech.com.

# **Packing List**

Before system installation, check that the items listed below are included and in good condition. If any item does not accord with the list, contact your dealer immediately.

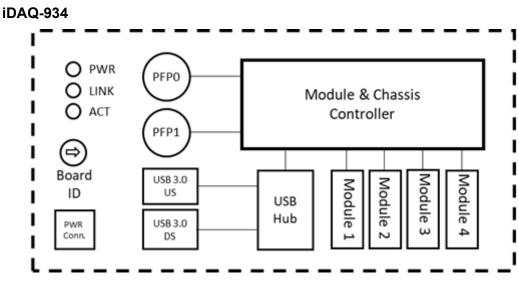

#### iDAQ-934

- iDAQ-934 x 1

- USB 3.0 Cable x 1

- 2-pin connector x 1

- DIN-Rail Kit x 2 (each set has screws x 2, frame x 1, buckle x 1)

- Startup Manual x 1

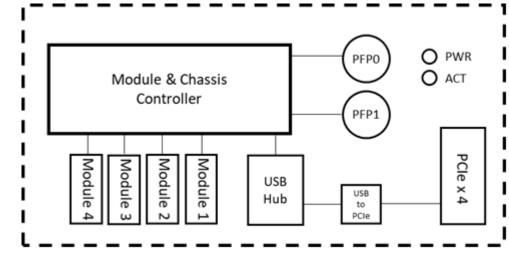

#### iDAQ-964

- iDAQ-964 x 1

- Screw x 3

- Startup Manual x 1

# **Safety Instructions**

- 1. Read these safety instructions carefully.

- 2. Retain this user manual for future reference.

- 3. Disconnect the equipment from all power outlets before cleaning. Use only a damp cloth for cleaning. Do not use liquid or spray detergents.

- 4. For pluggable equipment, the power outlet socket must be located near the equipment and easily accessible.

- 5. Protect the equipment from humidity.

- 6. Place the equipment on a reliable surface during installation. Dropping or letting the equipment fall may cause damage.

- 7. The openings on the enclosure are for air convection. Protect the equipment from overheating. Do not cover the openings.

- 8. Ensure that the voltage of the power source is correct before connecting the equipment to a power outlet.

- 9. Position the power cord away from high-traffic areas. Do not place anything over the power cord.

- 10. All cautions and warnings on the equipment should be noted.

- 11. If the equipment is not used for a long time, disconnect it from the power source to avoid damage from transient overvoltage.

- 12. Never pour liquid into an opening. This may cause fire or electrical shock.

- 13. Never open the equipment. For safety reasons, the equipment should be opened only by qualified service personnel.

- 14. If any of the following occurs, have the equipment checked by service personnel:

- The power cord or plug is damaged.

- Liquid has penetrated the equipment.

- The equipment has been exposed to moisture.

- The equipment is malfunctioning, or does not operate according to the user manual.

- The equipment has been dropped and damaged.

- The equipment shows obvious signs of breakage.

- 15. Do not leave the equipment in an environment with a storage temperature of below -20° C (-4° F) or above 60° C (140° F) as this may damage the components. The equipment should be kept in a controlled environment.

- 16. CAUTION: Batteries are at risk of exploding if incorrectly replaced. Replace only with the same or equivalent type as recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

- 17. In accordance with IEC 704-1:1982 specifications, the sound pressure level at the operator's position does not exceed 70 dB (A).

DISCLAIMER: These instructions are provided according to IEC 704-1 standards. Advantech disclaims all responsibility for the accuracy of any statements contained herein.

# **Safety Precautions - Static Electricity**

Follow these simple precautions to protect yourself from harm and the products from damage.

- To avoid electrical shock, always disconnect the power from the PC chassis before manual handling. Do not touch any components on the CPU card or other cards while the PC is powered on.

- Disconnect the power before making any configuration changes. A sudden rush of power after connecting a jumper or installing a card may damage sensitive electronic components.

# Contents

| Chapter | 1          | Start Using iDAQ Chassis1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

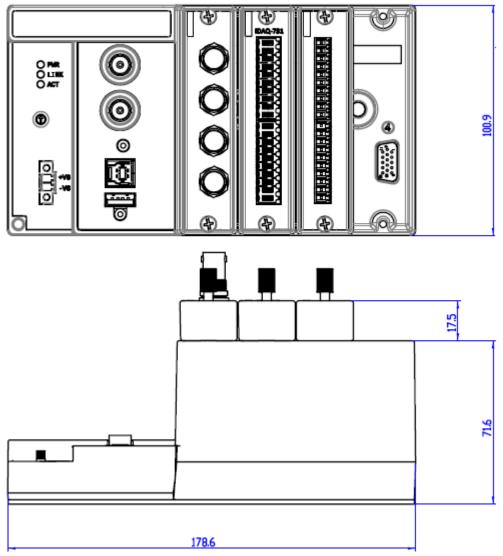

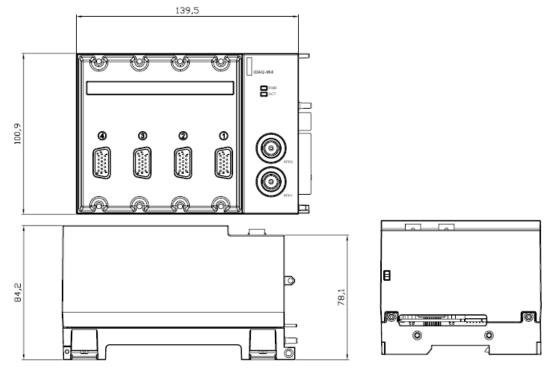

|         | 1.1<br>1.2 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

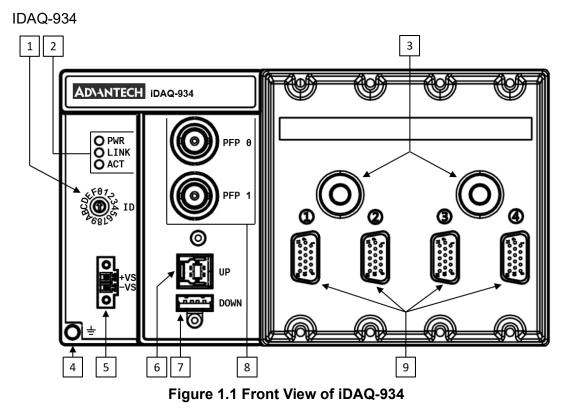

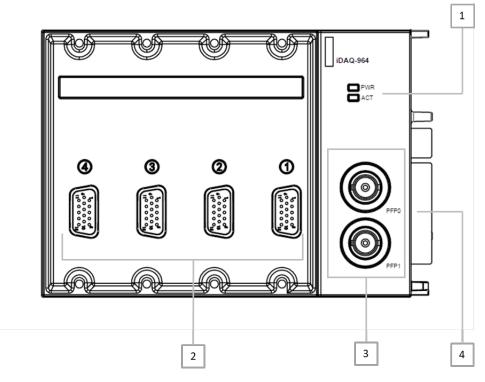

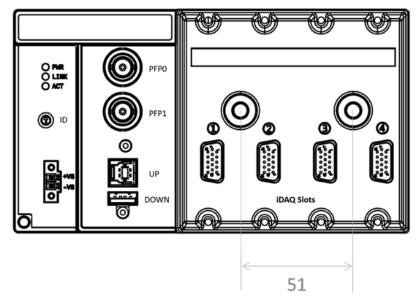

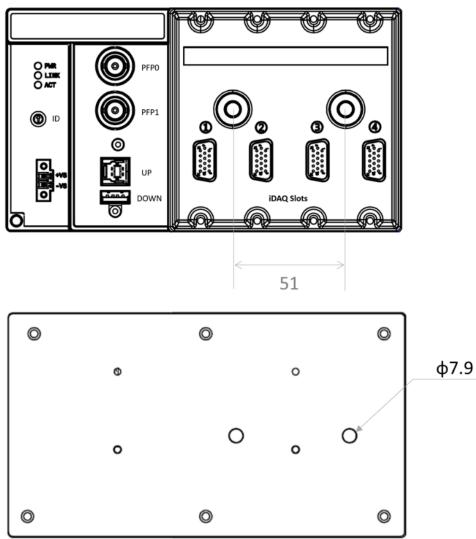

|         | 1.3        | Figure 1.2 Front View of iDAQ-9643Product Features41.3.1 Power Input41.3.2 Upstream USB Port41.3.3 Downstream USB Port41.3.4 LED Indicators41.3.5 Programmable Function Pin (PFP)4                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1.4        | 1.3.6Slots for IDAQ Modules41.3.7Board ID41.3.8Chassis Grounding Screw5Driver Installation5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |            | Figure 1.3 XNavi Installer5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 1.5<br>1.6 | Software Utilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1.7<br>1.8 | Application Software DAQNavi MCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1.9        | Accessories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter | 2          | Installation Guide7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

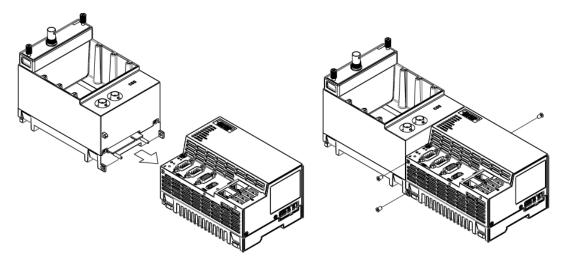

|         | 2.1        | Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

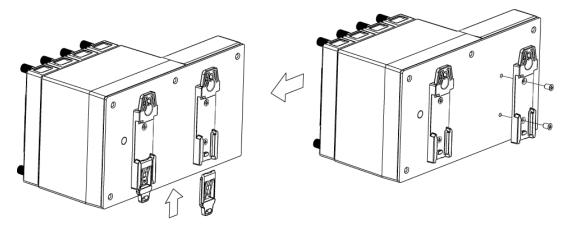

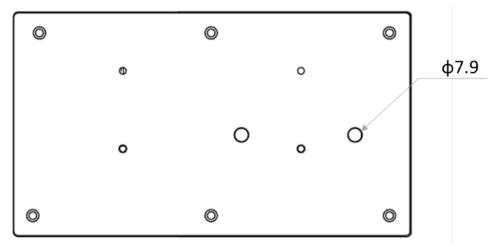

|         | 2.2        | Mounting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |            | Figure 2.2 DIN-Rail assembly for iDAQ-934                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

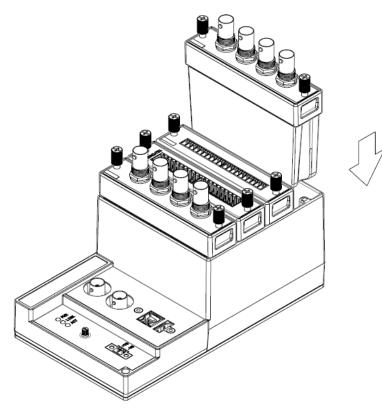

|         | 2.3        | Using iDAQ Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

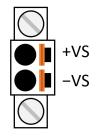

|         | 2.4        | Signal Connection and Pin Definition       12         2.4.1       Programmable Function Pin Connector       12         Figure 2.6       Pin assignment of PFP connector       12                                                                                                                                                                                                                                                                                                                                                                     |

|         |            | 2.4.2       Power Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter | 3          | Function Details13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

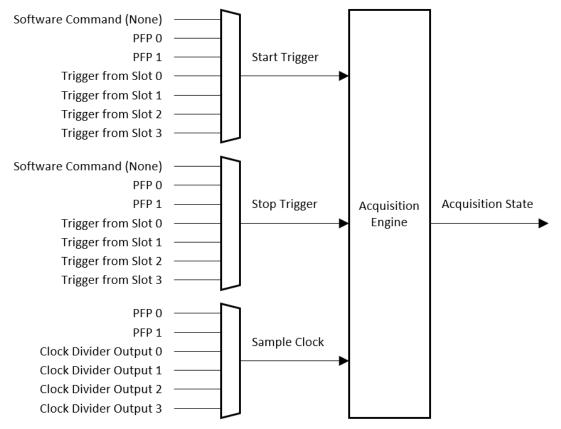

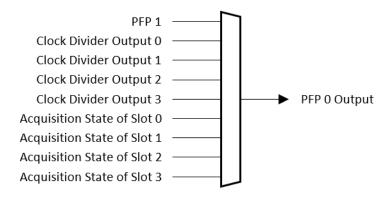

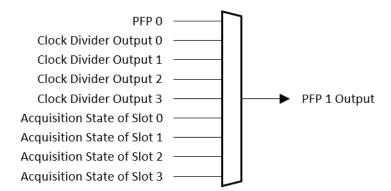

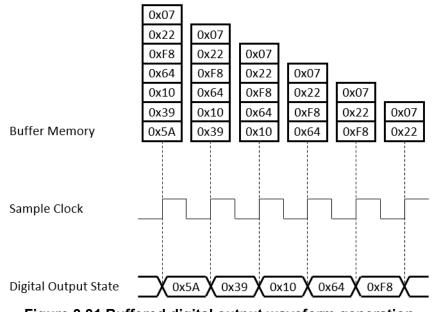

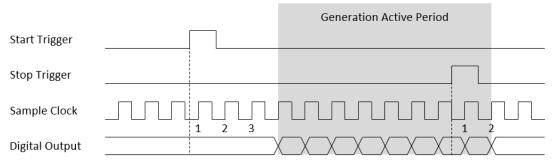

|         | 3.1<br>3.2 | Function Details       14         Trigger and Signal Routing       14         3.2.1       Signal Routing       14         Figure 3.1       Signal routing of an acquisition engine       14         3.2.2       Start Trigger and Stop Trigger       15         3.2.3       Sample Clock       15         3.2.4       Programmable Function Pin (PFP)       15         Figure 3.2       Signal routing for programmable function pin 0 as output       15         Figure 3.3       Signal routing for programmable function pin 1 as output       16 |

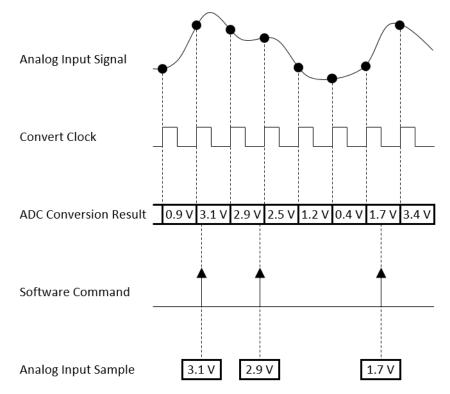

| 3.3 | Analog<br>3.3.1                                      | y Input<br>Instant Analog Input Acquisition<br>Figure 3.4 Instant analog input acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

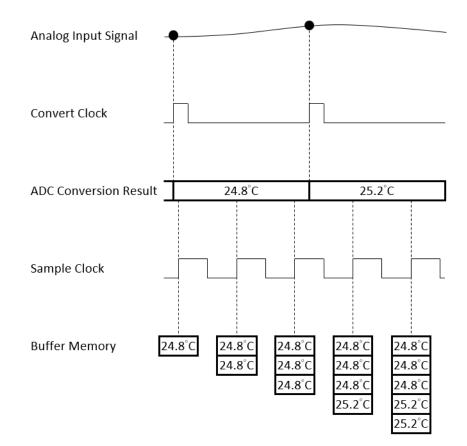

|     | 3.3.2                                                | Buffered Analog Input Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

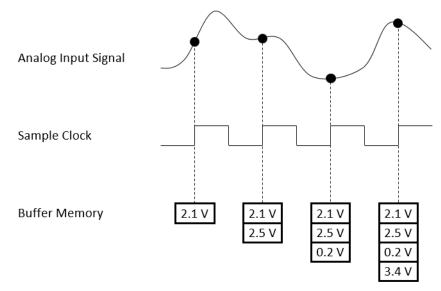

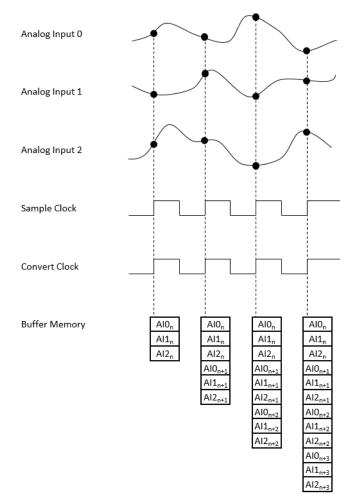

|     |                                                      | Figure 3.5 Buffered analog input acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

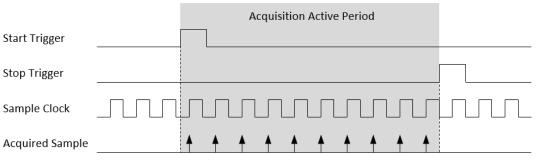

|     |                                                      | Figure 3.6 Start and stop of the analog input acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

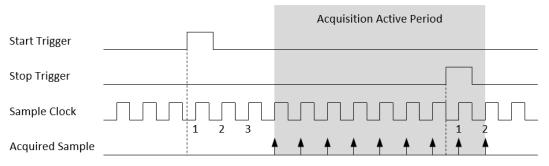

|     |                                                      | Figure 3.7 Start and stop of the analog input acquisition with 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.3.3                                                | Analog Input Convert Clock Signal Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

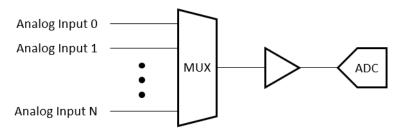

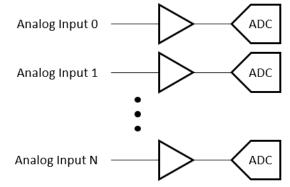

|     |                                                      | Figure 3.8 Multiplexed analog input module block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                      | Figure 3.9 Acquisition of a multiplexed analog input module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                      | Figure 3.10Simultaneously sampled analog input module bl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

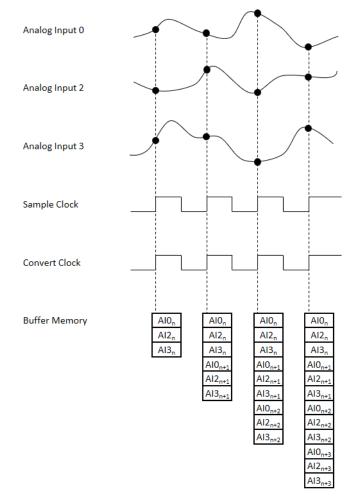

|     |                                                      | agram<br>Figure 3.11Acquisition of a simultaneously sampled analog<br>module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

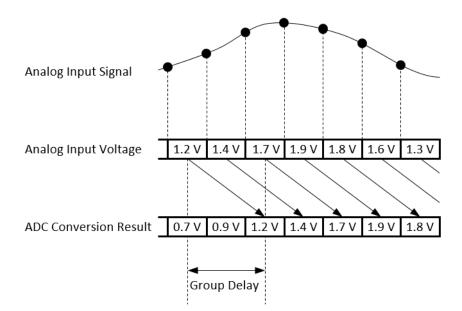

|     |                                                      | Figure 3.12Group delay of the sigma-delta ADC analog inpu<br>ule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t mod-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                      | Figure 3.13Acquisition of a low conversion rate ADC analog module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

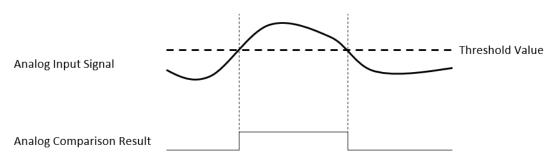

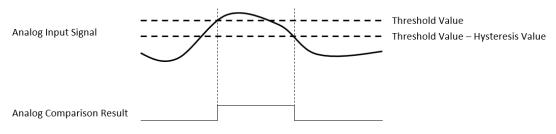

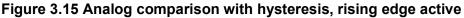

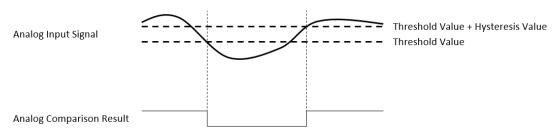

|     | 3.3.4                                                | Analog Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                      | Figure 3.14Analog comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                      | Figure 3.15Analog comparison with hysteresis, rising edge a 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                      | Figure 3.16Analog comparison with hysteresis, falling edge 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

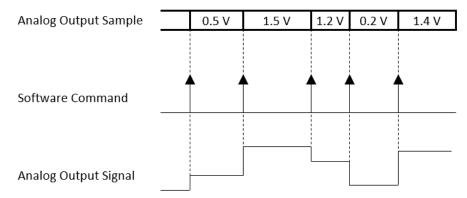

| 3.4 | -                                                    | y Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.4.1                                                | Static Analog Output Update<br>Figure 3.17Static analog output update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

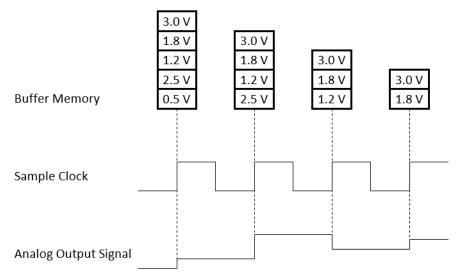

|     | 3.4.2                                                | Buffered Analog Output Waveform Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 0.1.2                                                | Figure 3.18Buffered analog output waveform generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

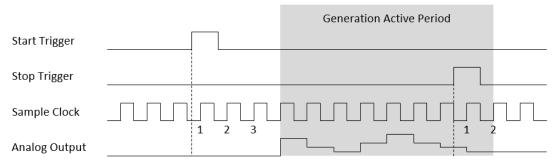

|     |                                                      | Figure 3.19Start and stop of the analog output waveform ge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                      | i igure o. Tootait and stop of the analog output wavelorm ge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | neia-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

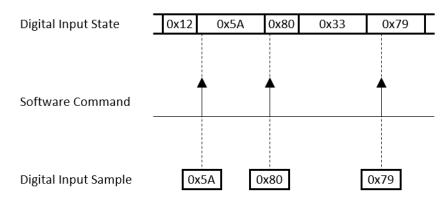

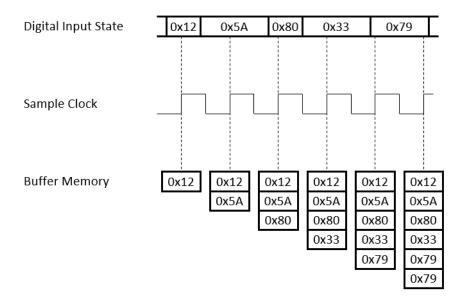

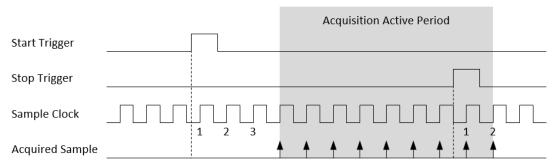

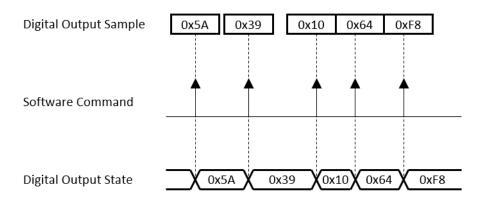

|     |                                                      | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |